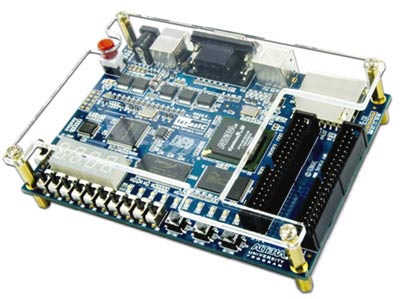

Плата DE0 для ознакомления и разработки

DE0 - плата для разработки и обучения выполнена в компактном форм-факторе. На ней установлены все дополнительные элементы, которые легко позволят даже новичкам получить представление о цифровых логических схемах, архитектуре компьютеров и микросхемах FPGA.

На плате смонтирована микросхема Altera Cyclone III 3C16 FPGA, которая содержит 15 408 логических элементов. Плата обеспечивает 346 пользовательских линий I/O, обладает большим набором возможностей, которые делают ее удобной для использования в расширенных курсах лекций в университетах и колледжах, а также при разработке сложных цифровых систем.

Плата DE0 объединяет малую потребляемую мощность, низкую стоимость и высокую производительность Altera Cyclone III FPGA для управления различными функциями платы DE0.

В комплект поставки, кроме самой платы разработки DE0 Development Board, входит программное обеспечение, образцы разработок и вспомогательные компоненты, необходимые для обеспечения простого доступа к плате DE0.

Отличительные особенности DE0:

- FPGA

- Cyclone III 3C16 FPGA

- 15 408 логических элементов,

- 56 M9K встроенных блоков памяти,

- 504 кБит общий объем ОЗУ,

- 56 встроенных преремножителей,

- 4 блока ФАПЧ,

- 346 пользовательских линии I/O,

- Корпус FineLine BGA с 484 выводами;

- Cyclone III 3C16 FPGA

- Память

- SDRAM

- Одна микросхема 8 МБайт синхронного динамического SDR ОЗУ;

- Flash память

- 4 МБайт NOR Flash-память,

- Поддерживает режим Байтов (8-битных)/Слов (16-битных);

- Гнездо для карт SD

- Обеспечивает как SPI, так и SD 1-bit режим доступа к SD картам;

- SDRAM

- Интерфейс

- Встроенная схема USB бластера

- Встроенный USB бластер для программирования,

- Построен на базе микросхемы Altera EPM240 CPLD;

- Последовательная микросхема для хранения конфигурации от Altera

- Микросхема последовательной EEPROM Altera EPCS4;

- Кнопки

- 3 кнопки;

- Движковые переключатели

- 10 движковых переключателей;

- Общий пользовательский интерфейс

- 10 светодиодов зеленого цвета свечения,

- четыре 7-сегментных индикатора,

- Интерфейс символьного ЖКИ 16x2 (без ЖКМ модуля);

- Входы тактирования

- 50 МГц генератор;

- VGA выход

- Использует 4-разрядный резисторный ЦАП,

- Сигналы выведены на 15-контактный разъем D-sub,

- Поддерживает разрешение до 1280x1024 при частоте кадровой развертки 60 Гц;

- Последовательные порты

- Один порт RS-232 (без разъема DB-9),

- Один порт PS/2 (можно использовать с PS/2 кабелем Y типа для подключения клавиатуры и мыши к одному порту);

- Два 40-контактных разъема расширения

- 72 линии I/O микросхемы Cyclone III, 8 линий питания и общей шины,

- 40-контактные разъемы предназначены для использования стандартного 40-жильного плоского кабеля, используемого для подключения IDE устройств.

- Встроенная схема USB бластера

Габаритные размеры

- Размеры: 99,7 х 128,02 мм.

Комплектация DE0:

- Плата DE0;

- USB кабель для программирования и управления FPGA;

- Системный CD для DE0, содержащий:

- оценочную копию среды разработки Altera's Quartus II Subscription & Web Edition and the Nios II Embedded Design Suit;

- документацию и материалы поддержки для DE0, включая Руководство Пользователя, утилиты для Панели Управления, образцы разработок и демонстрационные приложения, документацию на микросхемы;

- Прозрачный пластиковый корпус для платы;

- Сетевой адаптер постоянного тока с выходным напряжением 7,5 В.

Анонс стставил и подготовил

Андрей Самоделов,

contact@terraelectronica.ru

Производители: Terasic

Опубликовано: 18.11.2011