# EVAL-ADAU1372Z User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## **Evaluating the ADAU1372 Quad ADC, Dual DAC, Low Latency, Low Power Codec**

#### **EVAL-ADAU1372Z PACKAGE CONTENTS**

EVAL-ADAU1372Z evaluation board

EVAL-ADUSB2EBZ (USBi) communications adapter

USB cable with Mini-B plug

Evaluation board/software quick start guide

#### **DOCUMENTS NEEDED**

ADAU1372 data sheet

AN-1006 Application Note, *Using the EVAL-ADUSB2EBZ*

#### **GENERAL DESCRIPTION**

This user guide explains the design and setup of the EVAL-ADAU1372Z evaluation board.

This evaluation board provides full access to all analog and digital inputs/outputs on the ADAU1372. The ADAU1372 register can be controlled by Analog Devices, Inc., SigmaStudio™ software, which interfaces to the board via a USB connection. The EVAL-ADAU1372Z can be powered by a single AAA battery, by the USB bus, or by a single 3.8 V to 6 V supply; any of these are regulated to the voltages required on the board. The printed circuit board (PCB) is a 4-layer design, with a single ground plane and a single power plane on the inner layers. The board contains connectors for external microphones and speakers. The master clock can be provided externally or by the on-board 12.288 MHz passive crystal.

Note that throughout this application note, multifunction pins, such as SCL/SCLK, are referred to either by the entire pin name or by a single function of the pin, for example, SCLK, when only that function is relevant.

Complete specifications for the ADAU1372 are available in the ADAU1372 data sheet available from Analog Devices, and should be consulted in conjunction with this user guide when using the evaluation board.

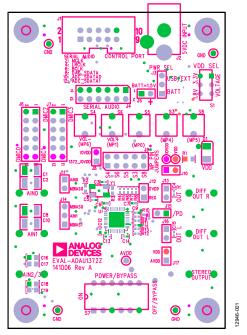

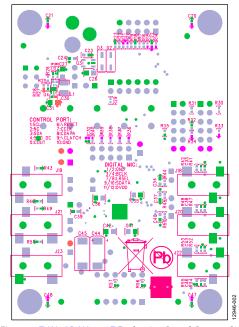

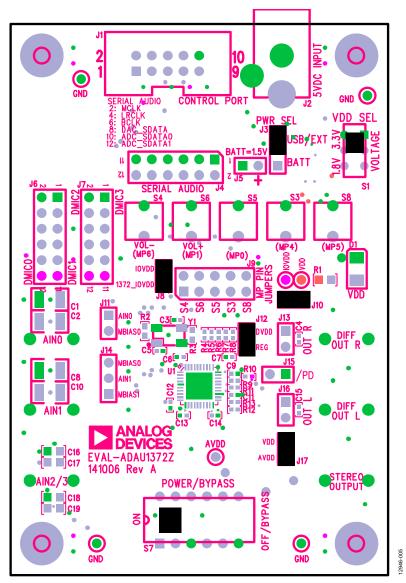

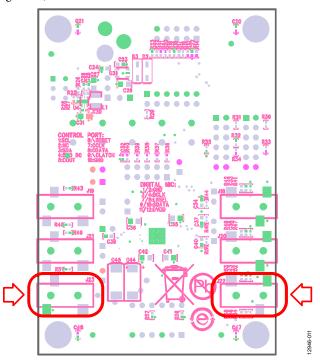

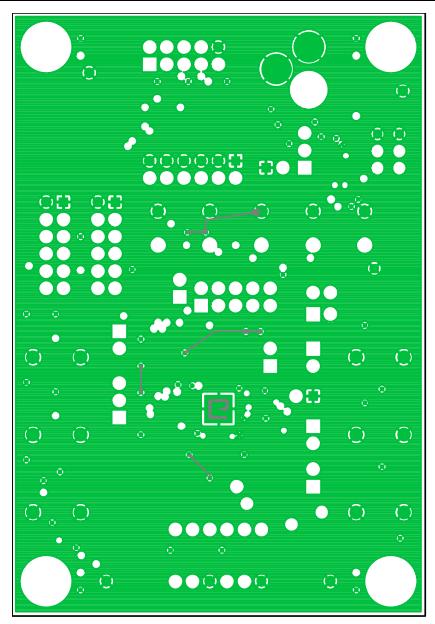

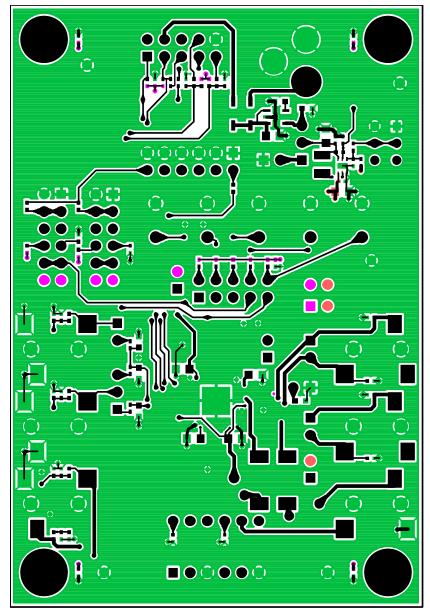

## EVAL-ADAU1372Z EVALUATION BOARD, TOP SIDE AND BOTTOM SIDE

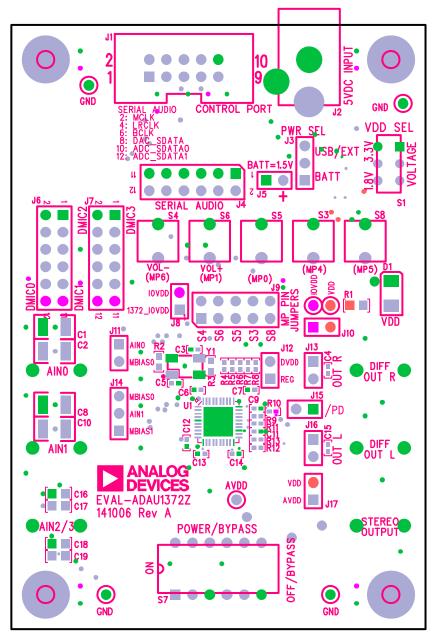

Figure 1. EVAL-ADAU1372Z Evaluation Board, Top Side

Figure 2. EVAL-ADAU1372Z Evaluation Board, Bottom Side

## **TABLE OF CONTENTS**

| EVAL-ADAU1372Z Package Contents                           | , ] |

|-----------------------------------------------------------|-----|

| Documents Needed                                          | . 1 |

| General Description                                       | . 1 |

| EVAL-ADAU1372Z Evaluation Board, Top Side and Bottom Side | . 1 |

| Revision History                                          | . 2 |

| Evaluation Board Block Diagrams                           | . 3 |

| Setting Up the Evaluation Board                           | . 5 |

| Installing the SigmaStudio Software                       | . 5 |

| Installing the USBi Drivers                               | . 5 |

| Default Switch and Jumper Settings                        | . 6 |

| Powering Up the Board                                     | . 6 |

| Connecting the Audio Cables                               | . 6 |

| Setting Up Communications in SigmaStudio                  | . 6 |

| Downloading the Default Settings                          | . 7 |

| Controlling Registers Using SigmaStudio | /  |

|-----------------------------------------|----|

| Using the Evaluation Board              | 8  |

| Power                                   | 8  |

| Inputs and Outputs                      | 8  |

| MPx Pins                                | 10 |

| Serial Audio Interface                  | 10 |

| Communications Header (J1)              | 12 |

| Power-Down                              | 12 |

| Hardware Description                    | 13 |

| Jumpers                                 | 13 |

| Integrated Circuits (IC)                | 13 |

| LED                                     | 13 |

| Evaluation Board Schematics and Artwork | 14 |

| Ordering Information                    | 23 |

| Bill of Materials                       |    |

#### **REVISION HISTORY**

2/15—Revision 0: Initial Version

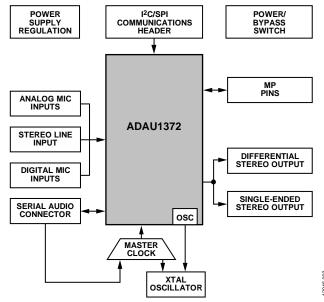

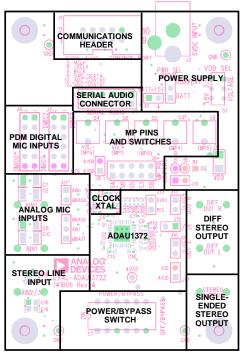

## **EVALUATION BOARD BLOCK DIAGRAMS**

Figure 3. Functional Block Diagram

Figure 4. Board Layout Block Diagram

Figure 5. Default Jumper and Switch Settings (Solid Black Rectangles Indicate Switch or Jumper Positions)

# SETTING UP THE EVALUATION BOARD INSTALLING THE SigmaStudio SOFTWARE

SigmaStudio must be installed to use the EVAL-ADAU1372Z.

Download the latest version of SigmaStudio by completing the following steps:

- 1. Create or log into your myAnalog account at analog.com.

- Download the SigmaStudio software from analog.com/SigmaStudioDownload.

- Install SigmaStudio by double clicking ADI\_SigmaStudioRel-<version>.exe and following the prompts. A computer restart is not required.

- 4. Consult ez.analog.com/community/dsp/SigmaDSP for answers to any questions.

#### **INSTALLING THE USBI DRIVERS**

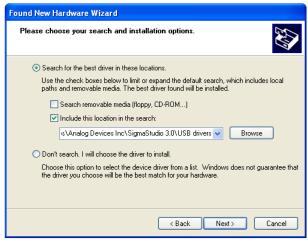

#### For Windows XP

SigmaStudio must be installed to use the USBi. When SigmaStudio has been properly installed, connect the USBi to an available USB port with the included USB cable. At this point, Windows® XP recognizes the device (see Figure 6) and prompts the user to install drivers.

Figure 6. Found New Hardware Notification

Click **Install from a list or specific location (Advanced)** and then click **Next** (see Figure 7).

Figure 7. Found New Hardware Wizard—Installation

Click Search for the best driver in these locations, select Include this location in the search, and click Browse to find the SigmaStudio 3.x\USB drivers directory (see Figure 8).

Figure 8. Found New Hardware Wizard—Search and Installation Options

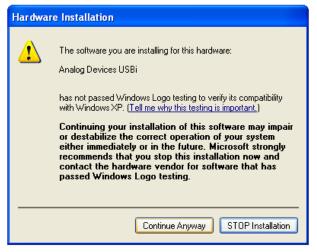

When the message about Windows logo testing appears, click **Continue Anyway** (see Figure 9).

Figure 9. Hardware Installation—Windows Logo Testing Warning

The USBi drivers are now installed. Leave the USBi connected to the PC.

#### For Windows 7 and Windows Vista

Connect the USBi to an available USB port with the included USB cable. At this point, Windows 7 recognizes the device and installs the drivers (see Figure 10).

Figure 10. USBi Driver Installed Correctly

#### **DEFAULT SWITCH AND JUMPER SETTINGS**

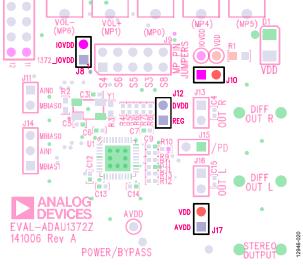

The J8, J10, J12, and J17 jumpers must be connected, and the J3 jumper must be set to the USB/EXT power setting. The MPx pin jumpers (J9) can be connected as desired to use the MPx push-buttons or switches. The microphone bias jumpers, J11 and J14, can be inserted if microphone bias is needed on Input 0 and Input 1.

Switch S7 selects whether the board is to be powered up or if audio is to be bypassed from input to output with the board powered down. For normal operation, slide the switch to the left. S1 selects whether the ADAU1372 is powered from 3.3 V or 1.8 V; the default is 3.3 V. When powering the board via the USBi, ensure that the switch on the bottom of the USBi board is set to the correct voltage (1.8 V or 3.3 V).

#### **POWERING UP THE BOARD**

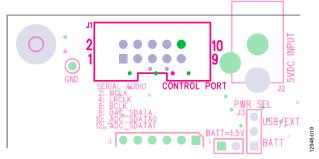

To power up the evaluation board, connect the ribbon cable of the USBi to J1 (CONTROL PORT) of the EVAL-ADAU1372Z.

#### **CONNECTING THE AUDIO CABLES**

Connect a stereo audio source to J22 (AIN2/3). Connect headphones or powered speakers to J23 (STEREO OUT). The labels for J22 and J23 are only visible on the bottom of the board (see Figure 11).

Figure 11. Stereo Out (J23), Left, and Stereo Input, AIN2/3 (J22), Right

#### **SETTING UP COMMUNICATIONS IN SigmaStudio**

Start SigmaStudio by double-clicking the shortcut on the desktop. To create a new project, click **New Project** in the **File** menu or press **CTRL** + **N**. The default view of the new project is called the Hardware Configuration tab.

To use the USBi in conjunction with SigmaStudio, select it in the Communication Channels subsection of the toolbox on the left side of the Hardware Configuration tab, and add it to the project space by clicking and dragging it to the right (see Figure 12).

Figure 12. Adding the USBi Communication Channel

If SigmaStudio cannot detect the USBi on the USB port of the PC, the background of the USB label is red (see Figure 13). This lack of communication can happen when the USBi is not connected or when the drivers are incorrectly installed.

Figure 13. USBi Not Detected by SigmaStudio

If SigmaStudio detects the USBi on the USB port of the PC, the background of the USB label changes to green (see Figure 14).

Figure 14. USBi Detected by SigmaStudio

To add an ADAU1372 to the project, select it from the **Processors** (**ICs/DSPs**) list and drag it to the project space (see Figure 15).

Figure 15. Adding an ADAU1372

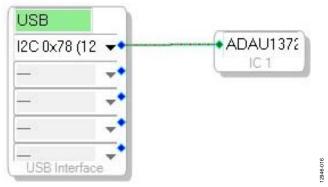

To use the USB interface to communicate with the target integrated circuit (IC), connect it by clicking and dragging a wire between the blue pin of the USBi and the green pin of the IC (see Figure 16). The corresponding list of the USBi automatically fills with the default mode and channel for that IC.

Figure 16. Connecting the USB Interface to an ADAU1372 IC

#### DOWNLOADING THE DEFAULT SETTINGS

The SigmaStudio default settings for the ADAU1372 set up the device to send the analog-to-digital converter (ADC) outputs to the serial ports in two I²S serial streams. The serial input port is routed to the two digital-to-analog converter (DAC) outputs. To update all of the registers with the default settings, click the Link-Compile-Download button once in the main toolbar of SigmaStudio (see Figure 17). Alternately, press F7.

Figure 17. Link-Compile-Download Button

After the download is complete, the registers for the ADAU1372 can be viewed and changed using SigmaStudio.

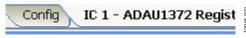

#### **CONTROLLING REGISTERS USING SigmaStudio**

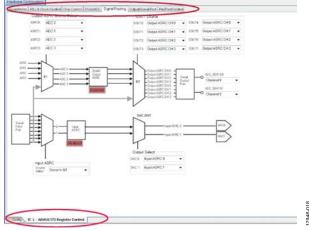

With SigmaStudio, users can view and change the register settings in real time. Click the **IC 1—ADAU1372 Register Control** tab on the bottom of the Hardware Configuration window to view and change the registers and to reveal the tabs on the top of the window used to view different groupings of registers (see Figure 18).

Figure 18. Hardware Configuration—Register Control in SigmaStudio

Clicking any of these register setting buttons or changing a drop-down box immediately changes the register setting. There is no need to click the **Link-Compile-Download** button again. The **Link-Compile-Download** button is useful for transferring all of the settings shown on every tab to the ADAU1372 with one click. Transferring the settings is a good thing to do when the device is first powered up. Until the **Link-Compile-Download** button is clicked, the settings of the device do not necessarily reflect the settings shown in SigmaStudio.

Alternatively, use the **Read All Registers** button to read the state of the device and update all of the objects in SigmaStudio. This button is often hidden from view and requires the user to scroll down to the bottom of the window. The **Link-Compile-Download** button is useful when working on hardware changes to quickly return the device to a known state after cycling the power.

The Capture window at the very bottom of the SigmaStudio window shows the registers that are being written when a control is activated.

One other detail about the link-compile-download function is that it properly sets the phase-locked loop (PLL) and main clock controls in the proper order to allow the PLL to lock and start up the internal clocks. The user is not required to select the proper sequence of controls to start up the ADAU1372.

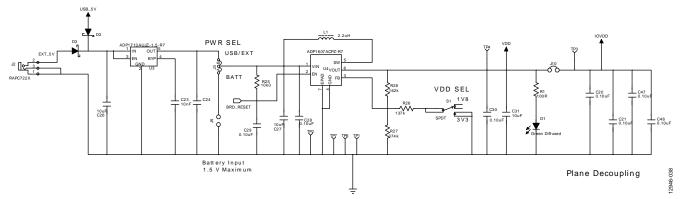

# USING THE EVALUATION BOARD POWER

Power can be supplied to the EVAL-ADAU1372Z in one of three ways. When Jumper J3 is in the USB/EXT position, power can be supplied by connecting the EVAL-ADUSB2EBZ (USBi) board to J1 (see Figure 19) or by connecting a tip positive 3.8 V dc to 6 V dc power supply on J2.

Figure 19. Header J1, Control Port

To supply power via a 1.5 V battery, J3 must be set to the BATT position, and the battery must be connected to J5. The on-board regulator generates the 3.3 V dc or 1.8 V dc supply, determined by S1, for the on-board circuitry. LED D1 lights up when power is supplied to the board. To connect power to the ADAU1372, connect the J8, J10, J12, and J17 jumpers (see Figure 20).

Figure 20. Power Jumpers

#### **INPUTS AND OUTPUTS**

The EVAL-ADAU1372Z has multiple audio input and output options, including digital and analog. There are four single-ended analog inputs that are configurable as microphone or line inputs, dual stereo digital microphone inputs, and two differential outputs that can also be used in a single-ended configuration.

#### **Analog Microphone Inputs**

For microphone signals, the ADAU1372 analog inputs can be configured as single-ended inputs with an optional programmable gain amplifier (PGA) mode.

#### **Microphone Bias**

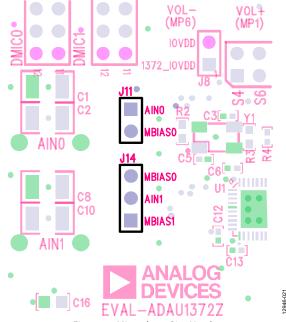

To add MBIAS0 to AIN0, connect a jumper to the J11 header. Similarly, MBIAS1 or MBIAS0 can be added to AIN1 by connecting a jumper to the J14 header (see Figure 21).

Figure 21. Microphone Bias Headers

Enable the microphone bias circuitry in the PGA/ADC tab of SigmaStudio to use it. The appropriate gain settings can also be chosen in this tab (see Figure 22).

Figure 22. Microphone Bias Enable and Gain

#### Stereo Line Input

The stereo input jack, J22, accepts a standard stereo TRS 1/8 inch mini-plug (tip is left, ring is right) with two channels of audio.

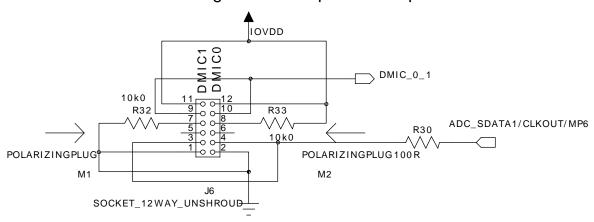

#### **Digital Microphones**

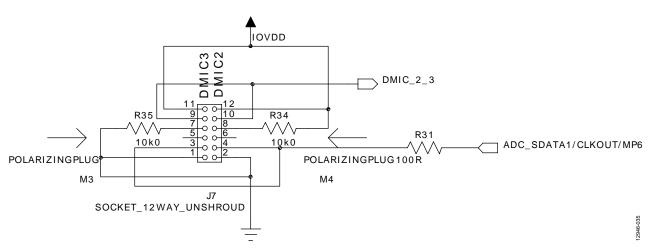

Pulse density modulated (PDM) digital microphones can be connected to standard 0.100 inch headers (J6 and J7). For example, the ADMP521 digital microphone from InvenSense plugs directly into the header.

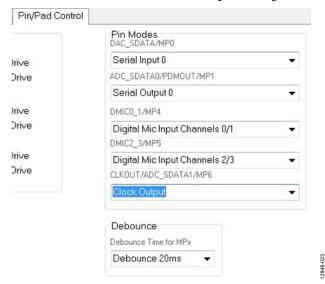

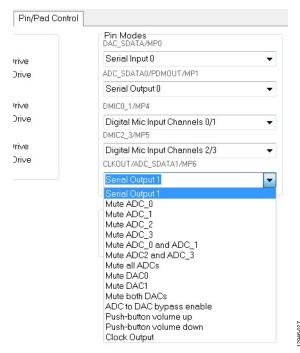

To use the digital microphone headers on the EVAL-ADAU1372Z, ensure that the proper settings are selected in SigmaStudio. Click the Pin/Pad Control tab. Change the value of the CLKOUT/ADC\_SDATA1/MP6 menu to Clock Output (see Figure 23).

Figure 23. Pin/Pad Control—MP6, Clock Output

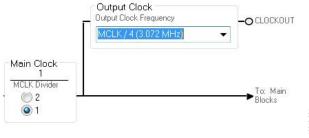

To set the value of BCLK, click the **PLL & Clock Control** tab and change the value of the **Output Clock Frequency** menu to the desired division on the internal master clock (MCLK) (see Figure 24).

Figure 24. Clock Output Enabled/Divided

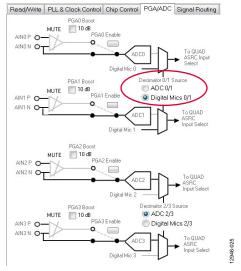

Next, set the input of the ADAU1372 to be the digital microphones instead of the ADCs by selecting the appropriate decimator source settings. Click the **PGA/ADC** tab to find and set the decimator source as shown in Figure 25.

Figure 25. Decimator Source

The digital microphones can then be routed via the appropriate inputs on the audio input cell.

#### **Headphone Output**

The headphone output, J23, connects to any standard 1/8 inch mini-plug stereo headphones. By setting the HP\_EN\_L and HP\_EN\_R bits in the headphone line output select register (Address 0x43), the output pins can be driven either by a line output driver or by a headphone driver. Headphones can be driven either as single-ended or differential outputs, and there are bits to disable the LN and RN pins if single-ended.

#### **Line Outputs**

The analog output pins, J19 and J21, can be used to drive differential loads. In their default settings, these pins can drive line loads of 10  $\Omega$  or greater.

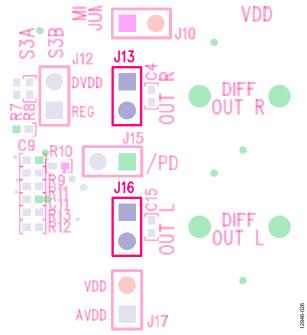

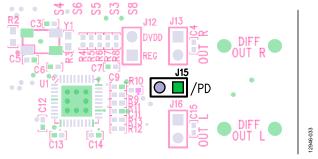

To use an external speaker, wires can be soldered to the unpopulated header pads, J13 and J16 (see Figure 26).

Figure 26. Unpopulated J13 and J16 Headers

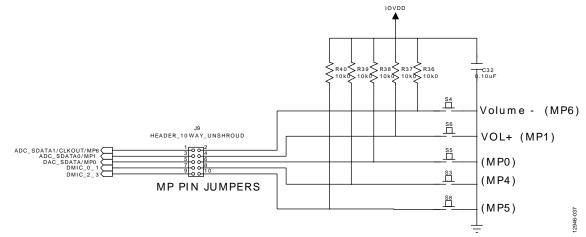

#### **MPx PINS**

The MPx pin jumpers, Header J9, provide access to the MPx pins (MP0, MP1, MP4, MP5, and MP6) of the ADAU1372, as well as facilitate the use of the push-buttons on the EVAL-ADAU1372Z evaluation board. See Figure 37 for the pinout of the header. These jumpers are used to enable the use of the volume control, mute, and other capabilities of the ADAU1372.

To use the full functionality of the MPx pins on the ADAU1372, change the selections in the menus under the Pin/Pad Control tab in the Hardware Configuration/ADAU1372 Register Control section of SigmaStudio. An example is shown in Figure 27.

Figure 27. Pin/Pad Control—Menus for MPx Pins

The MP4 and MP5 pins are connected to the digital microphone headers, J6 and J7, respectively. The MP6 pin also connects to both J6 and J7.

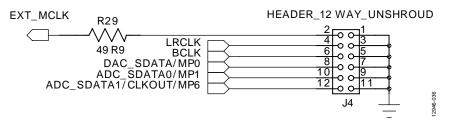

#### **SERIAL AUDIO INTERFACE**

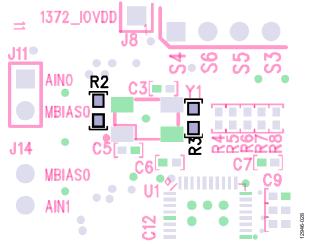

Serial audio signals in I<sup>2</sup>S, left justified, right justified, or timedivision multiplexing (TDM) format are available via the serial audio interface header, J4. This header also includes master clock input and output connection pins. To use MCLK on the J4 header, first install a resistor across the R2 pads. The R2 resistor is not populated from the factory. To use an external MCLK, remove the R3 resistor from the board to eliminate contention from the crystal oscillator on the MCLK line (see Figure 28).

Figure 28. R2 and R3

#### TDM/I<sup>2</sup>S Stream

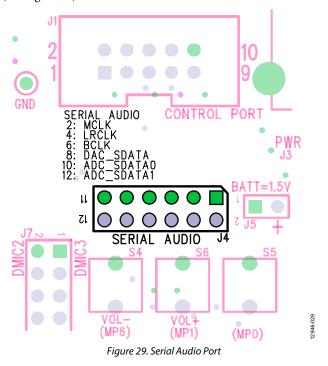

To use the serial audio outputs, connect the LRCLK, BCLK, and SDATA lines to the appropriate MPx pins on the evaluation board. The connections are located on the J4 header. The silk screen above the header helps identify where to connect the clocks and data (see Figure 29).

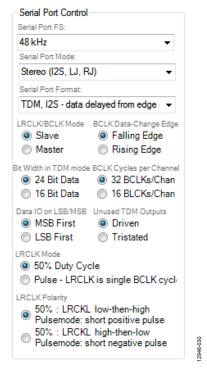

After connecting, use SigmaStudio to set the registers for the desired operation. In the Output/Serial Port tab, under the Serial Port Control section, the settings can be manipulated to create the specific data stream desired. These settings include serial port FS (sample rate), serial port mode, serial port format, LRCLK/BCLK mode (slave or master), BCLK data change edge, bit width in TDM mode, BCLK cycles per channel, data input/output on LSB/MSB, unused TDM outputs, LRCLK mode (as pulse or 50% duty cycle), and LRCLK polarity (see Figure 30).

Figure 30. Serial Port Control

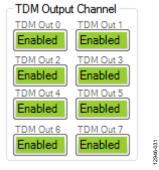

When using TDM mode, ensure that the appropriate TDM output channels are enabled in the TDM Output Channel section (see Figure 31).

Figure 31. TDM Output Channel

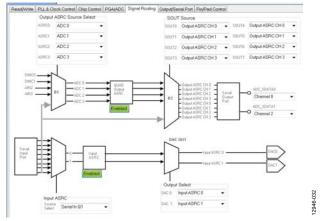

Use the Signal Routing tab to route the ADCs or serial inputs to either of the two available serial output lines. Ensure that quad output asynchronous sample rate converter (ASRC) is enabled (see Figure 32).

When using the serial input port, ensure that the input ASRC is enabled and select which TDM slots or I<sup>2</sup>S slots are output to the appropriate DAC outputs. The serial input stream can also be routed to the serial output stream, which allows the daisy-chaining of other ADC data into a TDM, 8-channel stream.

Figure 32. Signal Routing

#### **COMMUNICATIONS HEADER (J1)**

J1 connects to the EVAL-ADUSB2EBZ USBi. More information about the USBi can be found in the AN-1006 Application Note.

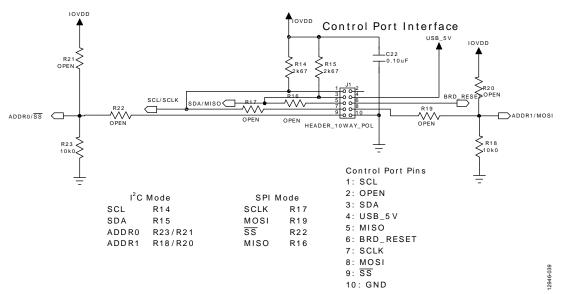

The IC defaults to I<sup>2</sup>C mode; however, it can be put into serial peripheral interface (SPI) control mode by pulling the  $\overline{SS}$  pin low three times.

#### **POWER-DOWN**

The power-down header, J15 (/PD), on the silkscreen of the board provides access to the power-down pin,  $\overline{PD}$ , on the ADAU1372. Put a jumper on the header to power down all analog and digital circuits. Before enabling the  $\overline{PD}$  pin, mute the outputs to avoid any pops or clicks when the IC is powered down (see Figure 33).

Figure 33. Power-Down Header J15

# HARDWARE DESCRIPTION JUMPERS

Table 1. Connector and Jack Descriptions

| Reference | Functional Name           | Description                                                                                                      |

|-----------|---------------------------|------------------------------------------------------------------------------------------------------------------|

| J1        | Control port              | The header facilitates communication between the evaluation board and USBi board.                                |

| J2        | 5 V dc input              | The connector provides external power to the board and accepts 3.8 V dc to 6 V dc input.                         |

| J3        | Power select              | The jumper is used to select power source for the evaluation board, selectable between USB/external and battery. |

| J4        | Serial audio              | The header accepts serial audio signals in I <sup>2</sup> S, left justified, right justified, or TDM format.     |

| J5        | Battery 1.5 V             | The jumper used to power the board via a 1.5 V battery.                                                          |

| J6, J7    | Digital microphone inputs | Headers that allow digital microphones to be connected to the evaluation board.                                  |

| J8        | IOVDD 1372_IOVDD          | The jumper supplies power to the IOVDD supply of the ADAU1372 from the power supply section.                     |

| J9        | MPx pin jumpers           | The jumpers used to connect push-buttons on the board to MPx pins on the ADAU1372.                               |

| J10       | IOVDD VDD                 | The jumper connects IOVDD on the ADAU1372 to VDD (3.3 V board supply) on the evaluation board.                   |

| J11, J14  | Microphone bias           | The jumpers used to add a microphone bias to the analog microphone inputs, AINO and AIN1.                        |

| J12       | DVDD regulator (REG)      | The jumper connects DVDD on the ADAU1372 to its internal regulator.                                              |

| J13       | Out R                     | The jumper provides access to the mono differential right channel output.                                        |

| J15       | Power down                | The jumper used to power down the ADAU1372 analog and digital circuits.                                          |

| J16       | Out L                     | The jumper provides access to the mono differential left channel output.                                         |

| J17       | VDD AVDD                  | The jumper connects AVDD on the ADAU1372 to VDD (3.3 V board supply) on the evaluation board.                    |

#### **INTEGRATED CIRCUITS (IC)**

#### **Table 2. IC Descriptions**

| Reference Functional Name |                                         | Description                                                                           |

|---------------------------|-----------------------------------------|---------------------------------------------------------------------------------------|

| U1                        | ADAU1372 codec                          | The codec being evaluated                                                             |

| U3                        | ADP1713AUJZ low dropout (LDO) regulator | Linear regulator that generates 1.5 V from an off board power supply                  |

| U4                        | ADP1607 boost regulator                 | Boost regulator that generates 1.8 V or 3.3 V for the board supply from a 1.5 V input |

#### **LED**

#### **Table 3. LED Description**

| Reference Functional Name Description |               | Description                                                  |

|---------------------------------------|---------------|--------------------------------------------------------------|

| D1                                    | VDD power LED | The LED illuminates when the evaluation board is powered up. |

# **EVALUATION BOARD SCHEMATICS AND ARTWORK** 12946-034 Mono Differential Output Left Mono Differential Output Right R57 49k9 R45 2k00 Stereo Analog Inputs 2&3 Analog Input 0 Analog Input

Figure 34. EVAL-ADAU1372Z Evaluation Board Schematic—Digital and Analog Input/Output, Master Clock Generation

## PDM Digital Microphone Inputs

Figure 35. EVAL-ADAU1372Z Evaluation Board Schematic—PDM Digital Microphone Interface

### Serial Audio Interface

Figure 36. EVAL-ADAU1372Z Evaluation Board Schematic --Serial Audio Interface

Figure 37. EVAL-ADAU1372Z Evaluation Board Schematic—MPx Pin Jumpers

Figure 38. EVAL-ADAU1372Z Evaluation Board Schematic—Power Supply

Figure 39. EVAL-ADAU1372Z Evaluation Board Schematic—Control Port Interface

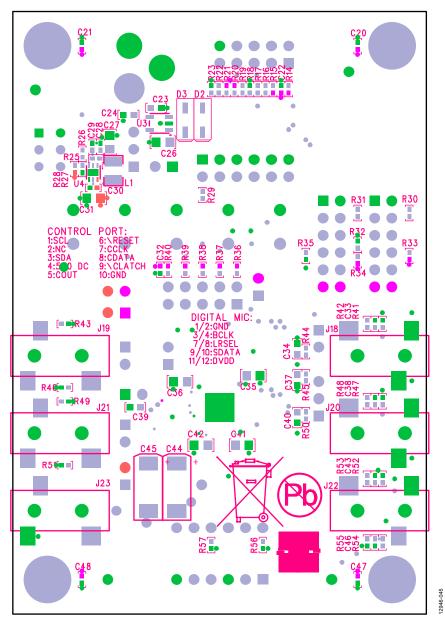

Figure 40. EVAL-ADAU1372Z Evaluation Board Layout—Top Assembly

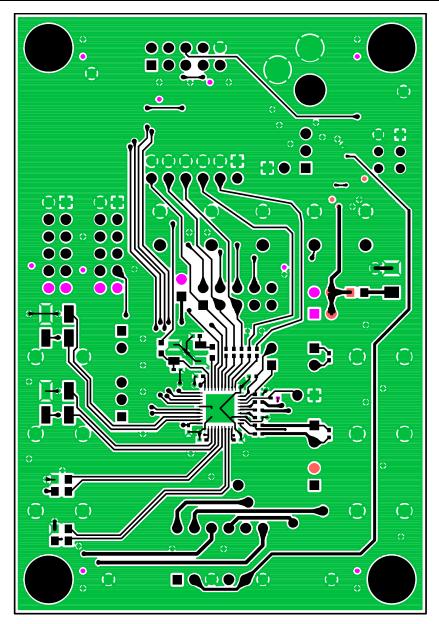

Figure 41. EVAL-ADAU1372Z Evaluation Board Layout—Top Copper

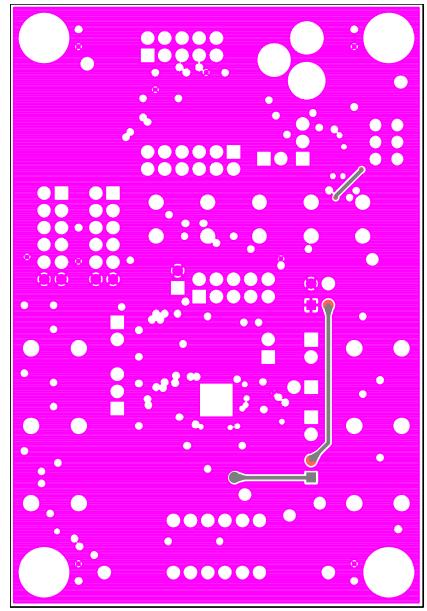

Figure 42. EVAL-ADAU1372Z Evaluation Board Layout—Power Plan, Layer 3

12946-04

Figure 43. EVAL-ADAU1372Z Evaluation Board Layout—Ground Plane, Layer 2

Figure 44. EVAL-ADAU1372Z Evaluation Board Layout—Bottom Copper

129

Figure 45. EVAL-ADAU1372Z Evaluation Board Layout—Bottom Assembly

# ORDERING INFORMATION BILL OF MATERIALS

Table 4.

|      | Table 4.                                                                |                                                                     |                               |                                |  |

|------|-------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|--------------------------------|--|

| Qty. | Designator                                                              | Description                                                         | Part Number                   | Manufacturer                   |  |

| 16   | C6 to C7, C9, C11 to C14,<br>C20 to C22, C28 to C30,<br>C32, C47 to C48 | 0.10 μF multilayer ceramic, 16 V, X7R (0402)                        | ECJ-0EX1C104K                 | Panasonic EC                   |  |

| 8    | R9, R11 to R13, R42, R48,<br>R53 to R54                                 | 0 Ω chip resistor, 5%, 63 mW, thick film, 0402                      | ERJ-2GE0R00X                  | Panasonic EC                   |  |

| 1    | C24                                                                     | 1.0 μF multilayer ceramic, 16 V, X7R, 0603                          | GRM188R71C105KA12D            | Murata ENA                     |  |

| 1    | C39                                                                     | 1.0 μF multilayer ceramic, 16 V, X7R, 0603                          | EMK107BJ105KA-TR              | Taiyo Yuden                    |  |

| 2    | R30, R31                                                                | $100 \Omega$ chip resistor, 1%, 63 mW, thick film, 0402             | MCR01MZPF1000                 | Rohm                           |  |

| 1    | R3                                                                      | $100 \Omega$ chip resistor, 1%, 100 mW, thick film, 0603            | ERJ-3EKF1000V                 | Panasonic EC                   |  |

| 1    | R1                                                                      | $100 \Omega$ chip resistor, 1%, 125 mW, thick film, 0805            | ERJ-6ENF1000V                 | Panasonic EC                   |  |

| 12   | R18, R23, R25, R32 to R40                                               | 10 kΩ chip resistor, 1%, 63 mW, thick film, 0402                    | MCR01MZPF1002                 | Rohm                           |  |

| 1    | C23                                                                     | 10 nF multilayer ceramic, 25 V, NP0, 0603                           | C1608C0G1E103J                | TDK Corporation                |  |

| 11   | C16 to C19, C26 to C27, C31,<br>C35 to C36, C41 to C42                  | 10 μF multilayer ceramic, 10 V, X7R, 0805                           | GRM21BR71A106KE51L            | Murata ENA                     |  |

| 1    | R26                                                                     | 137 kΩ chip resistor, 1%, 63 mW, thick film, 0402                   | ERJ-2RKF1373X                 | Panasonic ECG                  |  |

| 1    | R28                                                                     | 162 kΩ chip resistor, 1%, 63 mW, thick film, 0402                   | ERJ-2RKF1623X                 | Panasonic ECG                  |  |

| 1    | R10                                                                     | 1.00 kΩ chip resistor, 1%, 63 mW, thick film, 0402                  | ERJ-2RKF1001X                 | Panasonic EC                   |  |

| 3    | C34, C37, C40                                                           | 2.2 μF multilayer ceramic, 10 V, X7R, 0603                          | GRM188R71A225KE15D            | Murata ENA                     |  |

| 1    | L1                                                                      | 2.2 μH inductor                                                     | LQH32PN2R2NN0L                | Murata Electronics             |  |

| 2    | C3, C5                                                                  | 22 pF multilayer ceramic, 50 V, NP0, 0402                           | GRM1555C1H220JZ01D            | Murata ENC                     |  |

| 3    | R44 to R45, R50                                                         | 2.00 kΩ chip resistor, 1%, 63 mW, thick film, 0402                  | ERJ-2RKF2001X                 | Panasonic EC                   |  |

| 2    | R14 to R15                                                              | 2.67 kΩ chip resistor, 1%, 63 mW, thick film, 0402                  | CRCW04022K67FKED              | Vishay/Dale                    |  |

| 5    | R4 to R8                                                                | 33.2 Ω chip resistor, 1%, 63 mW, thick film, 0402                   | RMCF0402FT33R2                | Stackpole                      |  |

| 1    | R27                                                                     | 374 kΩ chip resistor, 1%, 63 mW, thick film, 0402                   | ERJ-2RKF3743X                 | Panasonic ECG                  |  |

| 2    | C44 to C45                                                              | 470 μF SMD tantalum capacitor, SMD D, 6.3 V                         | TR3D477M6R3C0200              | Vishay/Sprague                 |  |

| 4    | C1 to C2, C8, C10                                                       | 47.0 μF ceramic capacitor, 6.3 V, X7R, 1210                         | GCM32ER70J476KE19L            | Murata                         |  |

| 6    | R41, R47, R52, R55 to R57                                               | 49.9 kΩ chip resistor, 1%, 63 mW, thick film, 0402                  | CRCW040249K9FKED              | Vishay/Dale                    |  |

| 1    | R29                                                                     | 49.9 kΩ chip resistor, 1%, 63 mW, thick film, 0402                  | MCR01MZPF49R9                 | Rohm                           |  |

| 1    | S7                                                                      | Four-pole, double-throw slide switch vertical break-before-make     | ASE4204                       | Tyco Electronics               |  |

| 1    | Y1                                                                      | 12.288 MHz crystal, SMT, 18 pF                                      | ABM3B-12.288MHZ-10-1-U-T      | Abracon Corporation            |  |

| 1    | U1                                                                      | Quad ADC, dual DAC codec                                            | ADAU1372BCPZ                  | Analog Devices                 |  |

| 1    | U4                                                                      | Synchronous boost dc-to-dc converter                                | ADP1607ACPZ-R7                | Analog Devices                 |  |

| 1    | U3                                                                      | Fixed low dropout voltage regulator                                 | ADP1713AUJZ-1.5-R7            | Analog Devices                 |  |

| 1    | J1                                                                      | 10-way shroud polarized header, $2 \times 5$                        | N2510-6002RB                  | 3M                             |  |

| 1    | J9                                                                      | 10-way unshrouded jumper, 2 × 6                                     | PBC05DAAN or cut PBC36DAAN    | Sullins Connector<br>Solutions |  |

| 1    | J4                                                                      | 12-way unshrouded jumper                                            | PBC06DAAN or cut<br>PBC36DAAN | Sullins Connector<br>Solutions |  |

| 7    | J5, J8, J10 to J12, J15, J17                                            | 2-pin header, unshrouded jumper, 0.10 inch; use shunt Tyco 881545-2 | PBC02SAAN; or cut PBC36SAAN   | Sullins Connector<br>Solutions |  |

| 2    | J3, J14                                                                 | Three-position SIP header                                           | PBC03SAAN; or cut PBC36SAAN   | Sullins Connector<br>Solutions |  |

| 1    | D1                                                                      | Green diffused, 10 millicandela, 565 nm, 1206                       | SML-LX1206GW-TR               | Lumex Opto                     |  |

| 2    | D2 to D3                                                                | Schottky, 30 V, 0.5 A, SOD123 diode                                 | MBR0530T1G                    | On Semiconductor               |  |

| 6    | J18 to J23                                                              | Stereo mini jack                                                    | SJ-3523-SMT                   | CUI, Inc.                      |  |

| 10   | R16 to R17, R19 to R22,<br>R43, R46, R49, R51                           | Do not stuff                                                        | Open                          | Do not stuff                   |  |

| 1    | R2                                                                      | Do not stuff                                                        | Open                          | Do not stuff                   |  |

| 6    | C4, C15, C33, C38, C43, C46                                             | Do not stuff                                                        | Open                          | Do not stuff                   |  |

| 1    | J2                                                                      | Mini power jack, 0.08 inch, R/A, TH                                 | RAPC722X                      | Switchcraft                    |  |

Rev. 0 | Page 23 of 24

**UG-807**

## **EVAL-ADAU1372Z User Guide**

| Qty. | Designator  | Description                                     | Part Number    | Manufacturer         |

|------|-------------|-------------------------------------------------|----------------|----------------------|

| 2    | J6 to J7    | 12-way socket unshrouded, 2 × 6                 | PPPC062LFBN-RC | 3M                   |

| 1    | S1          | Single-pole, double-throw slide switch PC mount | EG1271         | E-Switch             |

| 5    | S3to S6. S8 | Tact switch long stroke (normally open)         | B3M-6009       | Omron Electronics    |

| 7    | TP1 to TP7  | Mini test point, white, 0.1 inch, OD            | 5002           | Keystone Electronics |

| 2    | J13, J16    | Do not stuff                                    | Open           | Do not stuff         |

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

#### **ESD Caution**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "ÁS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG12946-0-2/15(0)

www.analog.com