**Document status: Preliminary**

Copyright 2016 © Embedded Artists AB

# iMX6 SoloX COM Board Datasheet

Get Up-and-Running Quickly and Start Developing Your Application On Day 1!

#### **Embedded Artists AB**

Davidshallsgatan 16 211 45 Malmö Sweden

http://www.EmbeddedArtists.com

#### Copyright 2017 © Embedded Artists AB. All rights reserved.

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written permission of Embedded Artists AB.

#### **Disclaimer**

Embedded Artists AB makes no representation or warranties with respect to the contents hereof and specifically disclaim any implied warranties or merchantability or fitness for any particular purpose. The information has been carefully checked and is believed to be accurate, however, no responsibility is assumed for inaccuracies.

Information in this publication is subject to change without notice and does not represent a commitment on the part of Embedded Artists AB.

#### **Feedback**

We appreciate any feedback you may have for improvements on this document.

#### **Trademarks**

All brand and product names mentioned herein are trademarks, services marks, registered trademarks, or registered service marks of their respective owners and should be treated as such.

# **Table of Contents**

| 1     | Document Revision History                                         | 5  |

|-------|-------------------------------------------------------------------|----|

| 2     | Introduction                                                      | 6  |

| 2.1   | Hardware                                                          | 6  |

| 2.2   | Software                                                          | 7  |

| 2.3   | Features and Functionality                                        | 7  |

| 2.4   | Interface Overview                                                | 9  |

| 2.5   | Reference Documents                                               | 10 |

| 3     | EACOM Board Pinning                                               | 12 |

| 3.1   | Pin Numbering                                                     | 12 |

| 3.2   | Pin Assignment                                                    | 13 |

| 4     | Pin Mapping                                                       | 23 |

| 4.1   | Functional Multiplexing on I/O Pins                               | 23 |

| 4.1.1 | Alternative I/O Function List                                     | 23 |

| 4.2   | I/O Pin Control                                                   | 23 |

| 5     | Interface Description                                             | 24 |

| 5.1   | Analogue Inputs                                                   | 24 |

| 5.2   | Analogue Video Interface                                          | 24 |

| 5.3   | CAN                                                               | 25 |

| 5.4   | Display Interfaces                                                | 25 |

| 5.4.1 | Parallel RGB LCD Interface                                        | 26 |

| 5.4.2 | 2 LVDS Interface                                                  | 28 |

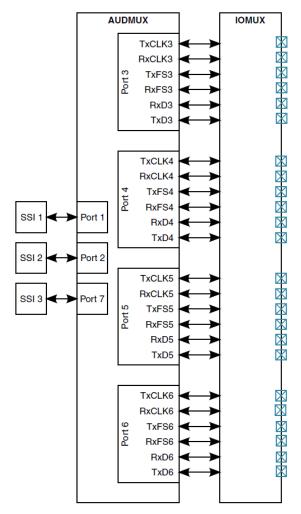

| 5.5   | Digital Audio Interfaces: Synchronous Serial Interface and AUDMUX | 29 |

| 5.6   | Digital Audio Interfaces: ESAI                                    | 33 |

| 5.7   | Digital Audio Interfaces: S/PDIF                                  | 34 |

| 5.8   | Digital Audio Interfaces: MQS                                     | 34 |

| 5.9   | Ethernet                                                          | 35 |

| 5.10  | GPIOs                                                             | 36 |

| 5.11  | I2C                                                               | 36 |

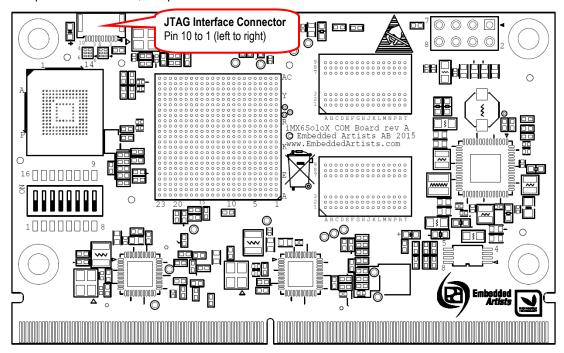

| 5.12  | JTAG                                                              | 38 |

| 5.13  | Matrix Keypad                                                     | 39 |

| 5.14  | PCI Express                                                       | 40 |

| 5.15  | Parallel Camera Interface                                         | 40 |

| 5.16  | Power Management                                                  | 43 |

| 5.17  | Power Supply Signals                                              | 43 |

| 5.18  | PWM                                                               | 44 |

| 5.19  | SD/MMC                                                            | 44 |

| 5.20  | SPI                                                               | 47 |

| 5.21  | UART                                                              | 48 |

| 5.22  | USB                                                   | 50 |

|-------|-------------------------------------------------------|----|

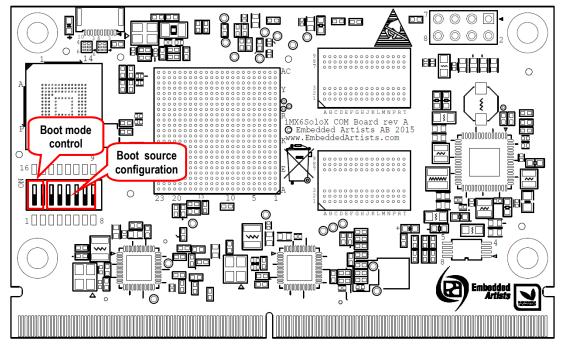

| 6     | Boot Options                                          | 52 |

| 6.1   | iMX6 SoloX COM Board, rev A, Boot Control Differences | 53 |

| 7     | Technical Specification                               | 55 |

| 7.1   | Absolute Maximum Ratings                              | 55 |

| 7.2   | Recommended Operating Conditions                      | 55 |

| 7.3   | Power Ramp-Up Time Requirements                       | 55 |

| 7.4   | Electrical Characteristics                            | 55 |

| 7.4.1 | Reset Output Voltage Range                            | 55 |

| 7.4.2 | Reset Input                                           | 56 |

| 7.4.3 | ADC_VREFH                                             | 56 |

| 7.5   | Power Consumption                                     | 56 |

| 7.6   | Mechanical Dimensions                                 | 56 |

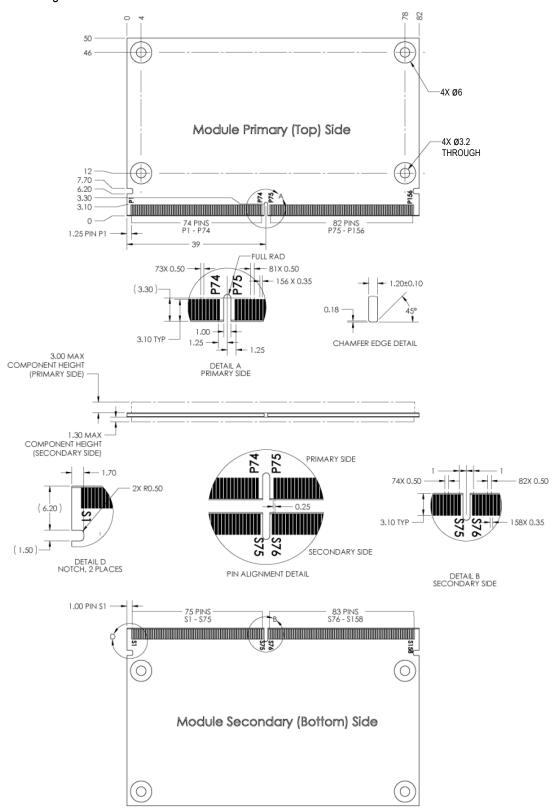

| 7.6.1 | MXM3 Socket                                           | 58 |

| 7.6.2 | Module Assembly Hardware                              | 58 |

| 7.7   | Environmental Specification                           | 58 |

| 7.7.1 | Operating Temperature                                 | 58 |

| 7.7.2 | Relative Humidity (RH)                                | 59 |

| 7.8   | Thermal Design Considerations                         | 59 |

| 7.8.1 | Thermal Management                                    | 59 |

| 7.8.2 | Thermal Parameters                                    | 59 |

| 7.9   | Product Compliance                                    | 59 |

| 8     | Functional Verification and RMA                       | 60 |

| 9     | Things to Note                                        | 61 |

| 9.1   | Shared Pins and Multiplexing                          | 61 |

| 9.2   | Only Use EA Board Support Package (BSP)               | 61 |

| 9.3   | OTP Fuse Programming                                  | 61 |

| 9.4   | Write Protect on Parameter Storage E2PROM             | 61 |

| 9.5   | Integration - Contact Embedded Artists                | 61 |

| 9.6   | ESD Precaution when Handling iMX6 SoloX COM Board     | 63 |

| 9.7   | EMC / ESD                                             | 63 |

| 10    | Custom Design                                         | 64 |

| 11    | Disclaimers                                           | 65 |

| 11.1  | Definition of Document Status                         | 66 |

# 1 Document Revision History

| Revision | Date       | Description                                                                                                      |

|----------|------------|------------------------------------------------------------------------------------------------------------------|

| PA1      | 2015-10-01 | First version.                                                                                                   |

| A        | 2016-07-18 | Updated to alphanumerical numbering of EACOM UART, SPI and I2C channels. Removed slide switches on rev A boards. |

| PB1      | 2017-07-31 | Added information about boot pins.                                                                               |

### 2 Introduction

This document is a datasheet that specifies and describes the *iMX6 SoloX COM Board* mainly from a hardware point of view. Some basic software related issues are also addressed, like booting and functional verification, but there are separate software development manuals that should also be consulted.

#### 2.1 Hardware

The *iMX6 SoloX COM Board* is a Computer-on-Module (COM) based on NXP's dual-core ARM Cortex-A9 / M4 i.MX 6SoloX System-on-Chip (SoC) application processor. The board provides a quick and easy solution for implementing a high-performance ARM dual-core Cortex-A9 / M4 based design. The Cortex-A9 runs at up to 1 GHz/800 MHz and the Cortex-M4 core at up to 227 MHz.

The dual-core architecture enables the system to run an OS like Linux on the Cortex-A9 and a Real-Time OS (RTOS) on the Cortex-M4. This architecture is ideal for real time applications where Linux cannot be used for all time critical task. The Cortex-M4 can handle (real time) critical tasks and can also be used to lower the power consumption.

The *iMX6 SoloX COM Board* delivers high computational and graphical performance at very low power consumption. The on-board PMIC, supporting DVFS (Dynamic Voltage and Frequency Scaling), together with a DDR3L memory sub-system reduce the power consumption to a minimum.

The SoC is part of the scalable i.MX6 product family. There is a range of iMX6 COM Boards from Embedded Artists with single, dual and quad Cortex-A9 cores. All boards share the same basic pinning (EACOM specification) for maximum flexibility and performance scalability.

The *iMX6 SoloX COM Board* has a very small form factor and shields the user from a lot of complexity of designing a high performance system. It is a robust and proven design that allows the user to focus the product development, shorten time to market and minimize the development risk.

The *iMX6 SoloX COM Board* targets a wide range of applications, such as:

- Industrial automation

- HVAC Building and Control Systems

- Smart Grid and Smart Metering

- HMI/GUI solutions

- Smart Toll Systems

- Connected vending machines

- Digital signage

- Point-of-Sale (POS) applications

- Data acquisition

- Communication gateway solutions

- Connected real-time systems

- Portable systems

- ...and much more

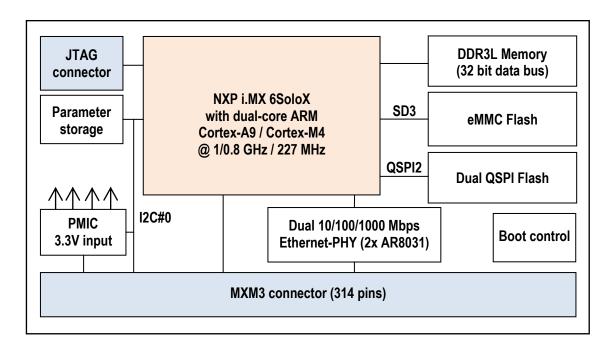

The picture below illustrates the block diagram of the iMX6 SoloX COM Board.

Figure 1 - iMX6 SoloX COM Board Block Diagram

The *iMX6 SoloX COM Board* pin assignment focus on direct connection to (carrier board) interface connectors and minimize trace and layer crossing. This is important for high speed, serial interfaces with impedance controlled differential pairs. As a result, carrier boards can be designed with few routing layers. In many cases, a four layer pcb is enough to implement advanced and compact carrier boards. The pin assignment is common for the *iMX6 COM Boards* from Embedded Artists and the general, so called, EACOM specification is found in separate document.

#### 2.2 Software

The iMX6 SoloX COM Board has Board Support Packages (BSPs) for Embedded Linux. Precompiled images are available. Embedded Artists works with partners that can provide support for other operating systems (OS). For more information contact Embedded Artists support.

This document has a hardware focus and does not cover software development. See other documents related to the iMX6 SoloX COM Board for more information about software development.

#### 2.3 Features and Functionality

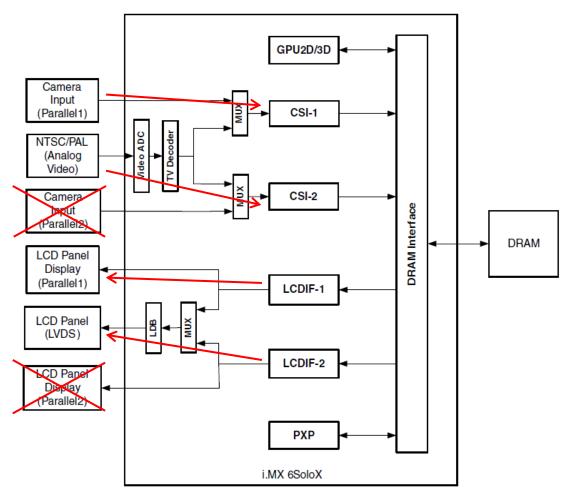

The i.MX 6SoloX is a powerful SoC. The full specification can be found in NXP's *iMX6 SoloX Datasheet* and *iMX6 SoloX Reference Manual*. The table below lists the main features and functions of the iMX6 SoloX COM board - which represents Embedded Artists integration of the iMX6 SoloX SoC. Due to pin configuration some functions and interfaces of the iMX6 SoloX are not available on the iMX6 SoloX COM board.

| Group | Feature           |                                                           | iMX6 SoloX COM Board                           |

|-------|-------------------|-----------------------------------------------------------|------------------------------------------------|

| CPUs  | NXP SoC           | commercial temperature range industrial temperature range | MCIMX6X4EVM10AB<br>MCIMX6X4CVM08AB             |

|       | CPU Cores         |                                                           | 1x Cortex-A9<br>1x Cortex-M4 with MPU/FPU      |

|       | L1 Instruction ca | ache                                                      | 32 KByte on Cortex-A9<br>16 KByte on Cortex-M4 |

|                    | L1 Data cache                                                                                  | 32 KByte on Cortex-A9<br>16 KByte on Cortex-M4   |

|--------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------|

|                    | L2 Cache on Cortex-A9                                                                          | 512 KByte                                        |

|                    | TCM on Cortex-M4                                                                               | 64 KByte                                         |

|                    | NEON SIMD media accelerator on Cortex-A9                                                       | ✓                                                |

|                    | Maximum CPU frequency (comm./ind. temp. range)                                                 | 996/792 MHz on Cortex-A9<br>227 MHz on Cortex-M4 |

| Security           | ARM TrustZone                                                                                  | ✓                                                |

| Functions          | Advanced High Assurance Boot                                                                   | ✓                                                |

|                    | Cryptographic Acceleration and Assurance Module                                                | ✓                                                |

|                    | Secure Non-Volatile Storage, incl. Secure Real-<br>Time Clock                                  | ✓                                                |

|                    | System JTAG controller                                                                         | ✓                                                |

| Memory             | DDR3L RAM Size                                                                                 | 1 GByte                                          |

|                    | DDR3L RAM Speed                                                                                | 800 MT/s                                         |

|                    | DDR3L RAM Memory Width                                                                         | 32 bit                                           |

|                    | eMMC NAND Flash (8 bit)                                                                        | 4 GByte                                          |

|                    | QSPI (two 4-bit in parallel)                                                                   | 64 MByte                                         |

| Graphical          | GPU 2D/3D                                                                                      | Vivante GC400T                                   |

| Processing         | Open GL ES 2.0 (17Mtri/s 133Mpxl/s)                                                            | ✓                                                |

|                    | PiXel Processing Pipeline (PXP)                                                                | ✓                                                |

| Graphical          | LVDS, 18/24-bit                                                                                | ✓                                                |

| Output             | RGB, 24-bit parallel interface                                                                 | ✓                                                |

| Graphical<br>Input | CMOS sensor interface (camera), digital 20-bit parallel interface                              | ✓                                                |

|                    | NTSC/PAL analogue video input interface (4 ch)                                                 | ✓                                                |

| Interfaces<br>(all | Dual 10/100/1000 Mbps Gigabit Ethernet controllers with support for Audio Video Bridging (AVB) | ✓ with on-board PHY                              |

| functions are not  | PCIe v2.0 (1 lane)                                                                             | ✓                                                |

| available at       | Dual 4 ch 12-bit ADC (8 ch in total)                                                           | ✓                                                |

| the same time)     | 2x USB 2.0 ports, HS OTG + PHY                                                                 | ✓                                                |

|                    | 3x SD/MMC 4.5                                                                                  | √ SD3 interface used on-board                    |

|                    | 5x SPI, 6x UART, 4x I <sup>2</sup> C, 5x I <sup>2</sup> S/SSI                                  | ✓                                                |

|                    | Dual FlexCAN, CAN bus 2.0B                                                                     | ✓                                                |

| Other              | PMIC (MMPF0200) supporting DVFS techniques for low power modes                                 | ✓                                                |

| On-board switches to select eMMC or QSPI boot source, or USB OTG booting                              | <b>√</b> |

|-------------------------------------------------------------------------------------------------------|----------|

| E2PROM storing board information including<br>Ethernet MAC address and memory bus setup<br>parameters | <b>√</b> |

| i.MX 6SoloX on-chip RTC                                                                               | ✓        |

| On-board watchdog functionality                                                                       | ✓        |

#### 2.4 Interface Overview

The table below lists the interfaces that are specified in the EACOM specification (see separate document for details) and what is supported by the iMX6 SoloX COM board.

| Interface        | EACOM specification                                                              | iMX6 SoloX COM<br>Board       | Note                                                                     |

|------------------|----------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------|

| UART             | 3 ports (two 4 wire and one 2 wire)                                              | 3 ports                       | More ports available as alternative pin functions                        |

| SPI              | 2 ports                                                                          | 2 ports                       | More ports available as alternative pin functions                        |

| I2C              | 3 ports                                                                          | 3 ports                       |                                                                          |

| SD/MMC           | 2 ports (one 4 databits and one 8 databits)                                      | 2 ports                       |                                                                          |

| Parallel LCD     | 24 databits and<br>CLK/HS/VS/DE                                                  | Full support                  |                                                                          |

| LCD support      | LCD power ctrl, Backlight power/contrast control, touch panel ctrl (RST and IRQ) | Full support                  | 1 PWM and 4 GPIO                                                         |

| LVDS LCD         | 2 ports (18/24 bit LVDS data)                                                    | 1 port                        |                                                                          |

| HDMI (TDMS)      |                                                                                  | -                             |                                                                          |

| Parallel Camera  |                                                                                  | 1 port                        |                                                                          |

| Serial Camera    | CSI, 4 lane                                                                      | -                             |                                                                          |

| Gigabit Ethernet | 2 ports                                                                          | 2 ports                       |                                                                          |

| PCle             | 1 post, 1 lane                                                                   | 1 port, 1 lane                |                                                                          |

| SATA             |                                                                                  | -                             |                                                                          |

| USB              | 1 USB3.0 OTG<br>1 USB3.0 Host<br>1 USB2.0 Host                                   | 1 USB2.0 OTG<br>1 USB2.0 Host |                                                                          |

| SPDIF            | 1 TX/RX port                                                                     | 1 port                        |                                                                          |

| CAN              | 2 ports                                                                          | 2 ports                       |                                                                          |

| I2S/SSI/AC97     | 1 port (4 wire synchronous plus MCLK)                                            | 1 port                        | Shared pins are used. More ports available as alternative pin functions. |

| Analog audio  | Stereo output           | -                          |                                                                      |

|---------------|-------------------------|----------------------------|----------------------------------------------------------------------|

| GPIO          | 9 pins                  | 7 pins                     | More GPIO pins are available as alternative pin functions.           |

| PWM           | 1 pin                   | 1 pin                      | More pins are available as alternative pin functions.                |

| ADC           | 8 inputs                | 8 inputs                   |                                                                      |

| Type specific | 39 pins                 | 4 Video ADC inputs         | 35 type specific pins not used since all i.MX 6SoloX pins allocated. |

| Power         | 10 VIN, VBAT and 47 GND | 10 VIN, VBAT and<br>47 GND | About 15% of the pins are ground pins.                               |

#### 2.5 Reference Documents

The following documents are important reference documents and should be consulted when integrating the iMX6 SoloX COM board:

- EACOM Board Specification

- EACOM Board Integration Manual

The following NXP documents are also important reference documents and should be consulted for functional details:

- IMX6SXCEC, i.MX 6SoloX Applications Processors for Consumer Products Data Sheet, latest revision

- IMX6SXRM, i.MX 6SoloX Applications Processor Reference Manual, latest revision

- IMX6SXCE, Chip Errata for the i.MX 6SoloX, latest revision

Note: It is the user's responsibility to make sure all errata published by the manufacturer are taken note of. The manufacturer's advice should be followed.

- AN5050, i.MX 6SoloX Power Consumption Measurement, latest revision

- AN5062, i.MX 6SoloX Product Lifetime Usage Estimates, latest revision

The following documents are external industry standard reference documents and should also be consulted when applicable:

- eMMC (Embedded Multi-Media Card) the eMMC electrical standard is defined by JEDEC JESD84-B45 and the mechanical standard by JESD84-C44 (www.jedec.org)

- GbE MDI (Gigabit Ethernet Medium Dependent Interface) defined by IEEE 802.3. The 1000Base-T operation over copper twisted pair cabling is defined by IEEE 802.3ab (www.ieee.org)

- The I2C Specification, Version 2.1, January 2000, Philips Semiconductor (now NXP) (www.nxp.com)

- I2S Bus Specification, Feb. 1986 and Revised June 5, 1996, Philips Semiconductor (now NXP) (www.nxp.com)

- JTAG (Joint Test Action Group) defined by IEEE 1149.1-2001 IEEE Standard Test Access Port and Boundary Scan Architecture (www.ieee.org)

- MXM3 Graphics Module Mobile PCI Express Module Electromechanical Specification, Version 3.0, Revision 1.1, © 2009 NVIDIA Corporation (www.mxm-sig.org)

- PCI Express Specifications (www.pci-sig.org)

- SD Specifications Part 1 Physical Layer Simplified Specification, Version 3.01, May 18, 2010,

© 2010 SD Group and SD Card Association (Secure Digital) (www.sdcard.org)

- SPDIF (aka S/PDIF) (Sony Philips Digital Interface) IEC 60958-3

- SPI Bus "Serial Peripheral Interface" de-facto serial interface standard defined by Motorola. A good description may be found on Wikipedia (http://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface\_Bus)

- USB Specifications (www.usb.org)

## 3 EACOM Board Pinning

Embedded Artists has defined the EACOM board standard that is based on the SMARC form factor; module size 82 x 50 mm. Note that pinning is different from the SMARC standard. See the *EACOM Board specification* document for details and background information. Hereafter this standard will be referred to as **EACOM**.

The carrier board connector has 314 pins with 0.5 mm pitch and the COM board is inserted in a right angle (R/A) style. The connector is originally defined for use with MXM3 graphics cards. There are multiple sources for carrier board (MXM3) connectors due to the popular standard. The signal integrity is excellent and suitable for data rates up to 5 GHz.

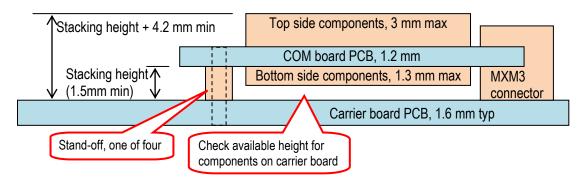

Overall assembly height of the COM board/Carrier board connector can be as low as 6 mm. There are different stack height options available, including 2.7 mm (resulting in overall 6 mm height), 5 mm and 8 mm.

#### 3.1 Pin Numbering

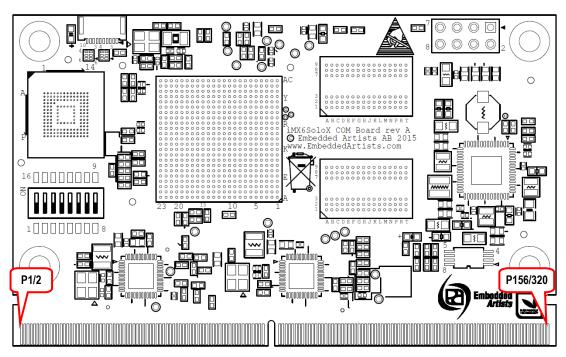

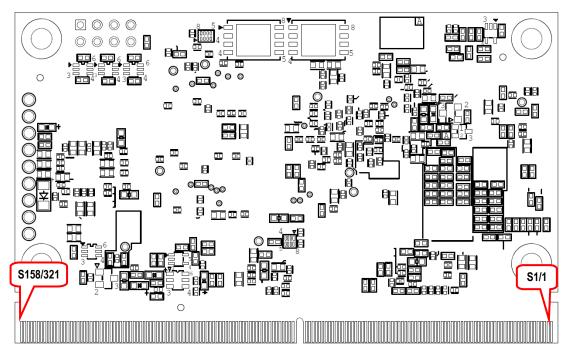

The figures below show the pin numbering for EACOM. Top side edge fingers are numbered P1-P156. Bottom side edge fingers are numbered S1-S158. There is an alternative pin numbering that follows the MXM3 standard with even numbers on the bottom and odd numbers on the top. This numbering is from 1-321, with 7 numbers/pins (150-156) removed due to the keying.

Figure 2 - EACOM Board Pin Numbering, Top Side

Figure 3 - EACOM Board Pin Numbering, Bottom Side

#### 3.2 Pin Assignment

This section describes the pin assignment of the board, with the following columns:

Pin number Px are top side edge fingers. Sx are bottom side edge fingers. An

alternative, consecutive, numbering is also shown with odd numbers

on the top and even numbers on the bottom side.

EACOM Board Describe the typical usage of the pin according to EACOM. This pin

usage should be followed to get compatibility between different COM boards. If this is not needed, then any of the alternative functions on

the pin can also be used.

i.MX 6SoloX Ball Name The name of the ball of the i.MX 6SoloX SoC (or other component on

the COM board) that is connected to this pin.

Notes When relevant, the preferred pin function is listed.

There are 47 ground pins, which equal to about 15%, and 10 input voltage supply pins.

Note that some pins are COM board *type specific*, meaning that these pins might not be compatible with other EACOM boards. Using these may result in lost compatibility between EACOM boards, but not always. Check details between EACOM boards of interest.

The table below lists the top side pins, P1-P156, odd numbers.

| Top Side<br>Pin Number | EACOM Board | i.MX 6SoloX Ball<br>Name | Alternative pin functions? | Notes                                                   |

|------------------------|-------------|--------------------------|----------------------------|---------------------------------------------------------|

| P1/2                   | GPIO6       | KEY_ROW2                 | Yes                        | GPIO6 controlled by alternative pin function GPIO2_IO17 |

| P2/4                   | GPIO5       | KEY_COL2                 | Yes                        | GPIO5 controlled by alternative pin function GPIO2_IO12 |

| P3/6                   | GPIO4       | KEY_ROW1                 | Yes                        | GPIO4 controlled by alternative pin function GPIO2_IO16 |

| P4/8                   | GPIO3       | SD4_RESET                | Yes                        | GPIO3 controlled by alternative pin function GPIO6_IO22 |

| P5/10                  | SD_D1       | SD2_DATA1                | Yes                        |                                                         |

| P6/12  | SD_D0         | SD2_DATA0 | Yes |                                                                                  |

|--------|---------------|-----------|-----|----------------------------------------------------------------------------------|

| P7/14  | SD_CLK        | SD2_CLK   | Yes |                                                                                  |

| P8/16  | SD_CMD        | SD2_CMD   | Yes |                                                                                  |

| P9/18  | SD_D3         | SD2_DATA3 | Yes |                                                                                  |

| P10/20 | SD_D2         | SD2_DATA2 | Yes |                                                                                  |

| P11/22 | SD_VCC        |           |     | Supply voltage for SD interface (3.1-3.3V). Should only supply the SD interface. |

| P12/24 | MMC_D1        | SD4_DATA1 | Yes |                                                                                  |

| P13/26 | MMC_D0        | SD4_DATA0 | Yes |                                                                                  |

| P14/28 | MMC_D7        | SD4_DATA7 | Yes |                                                                                  |

| P15/30 | MMC_D6        | SD4_DATA6 | Yes |                                                                                  |

| P16/32 | MMC_CLK       | SD4_CLK   | Yes |                                                                                  |

| P17/34 | MMC_D5        | SD4_DATA5 | Yes |                                                                                  |

| P18/36 | MMC_CMD       | SD4_CMD   | Yes |                                                                                  |

| P19/38 | MMC_D4        | SD4_DATA4 | Yes |                                                                                  |

| P20/40 | MMC_D3        | SD4_DATA3 | Yes |                                                                                  |

| P21/42 | MMC_D2        | SD4_DATA2 | Yes |                                                                                  |

| P22/44 | GND           |           |     |                                                                                  |

| P23/46 | HDMI_TXC_N    |           |     | HDMI interface not assigned on this COM board.                                   |

| P24/48 | HDMI_TXC_P    |           |     | HDMI interface not assigned on this COM board.                                   |

| P25/50 | GND           |           |     |                                                                                  |

| P26/52 | HDMI_TXD0_N   |           |     | HDMI interface not assigned on this COM board.                                   |

| P27/54 | HDMI_TXD0_P   |           |     | HDMI interface not assigned on this COM board.                                   |

| P28/56 | HDMI_HPD      |           |     | HDMI interface not assigned on this COM board.                                   |

| P29/58 | HDMI_TXD1_N   |           |     | HDMI interface not assigned on this COM board.                                   |

| P30/60 | HDMI_TXD1_P   |           |     | HDMI interface not assigned on this COM board.                                   |

| P31/62 | GND           |           |     |                                                                                  |

| P32/64 | HDMI_TXD2_N   |           |     | HDMI interface not assigned on this COM board.                                   |

| P33/66 | HDMI_TXD2_P   |           |     | HDMI interface not assigned on this COM board.                                   |

| P34/68 | HDMI_CEC      |           |     | HDMI interface not assigned on this COM board.                                   |

| P35/70 | GND           |           |     |                                                                                  |

| P36/72 | ETH1_MD1_P    |           |     | Connects to Ethernet-PHY AR8031 #1, pin 14                                       |

| P37/74 | ETH1_MD1_N    |           |     | Connects to Ethernet-PHY AR8031 #1, pin 15                                       |

| P38/76 | GND           |           |     |                                                                                  |

| P39/78 | ETH1_MD0_P    |           |     | Connects to Ethernet-PHY AR8031 #1, pin 11                                       |

| P40/80 | ETH1_MD0_N    |           |     | Connects to Ethernet-PHY AR8031 #1, pin 12                                       |

| P41/82 | ETH1_LINK1000 |           |     | Connects to Ethernet-PHY AR8031 #1, pin 24                                       |

| P42/84 | ETH1_ACT      |           |     | Connects to Ethernet-PHY AR8031 #1, pin 23                                       |

| P43/86 | ETH1_LINK     |           |     | Connects to Ethernet-PHY AR8031 #1, pin 26                                       |

| P44/88 | ETH1_MD3_N    |           |     | Connects to Ethernet-PHY AR8031 #1, pin 21                                       |

| P45/90 | ETH1_MD3_P    |           |     | Connects to Ethernet-PHY AR8031 #1, pin 20                                       |

| P46/92 | GND           |           |     |                                                                                  |

|        |               |           |     |                                                                                  |

| P47/94  | ETH1_MD2_N       |               |     | Connects to Ethernet-PHY AR8031 #1, pin 18                                         |

|---------|------------------|---------------|-----|------------------------------------------------------------------------------------|

| P48/96  | ETH1_MD2_P       |               |     | Connects to Ethernet-PHY AR8031 #1, pin 17                                         |

| P49/98  | GND              |               |     |                                                                                    |

| P50/100 | ETH2_MD1_P       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 14                                         |

| P51/102 | ETH2_MD1_N       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 15                                         |

| P52/104 | GND              |               |     |                                                                                    |

| P53/106 | ETH2_MD0_P       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 11                                         |

| P54/108 | ETH2_MD0_N       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 12                                         |

| P55/110 | ETH2_LINK1000    |               |     | Connects to Ethernet-PHY AR8031 #1, pin 24                                         |

| P56/112 | ETH2_ACT         |               |     | Connects to Ethernet-PHY AR8031 #2, pin 23                                         |

| P57/114 | ETH2_LINK        |               |     | Connects to Ethernet-PHY AR8031 #2, pin 26                                         |

| P58/116 | ETH2_MD3_N       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 21                                         |

| P59/118 | ETH2_MD3_P       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 20                                         |

| P60/120 | GND              |               |     |                                                                                    |

| P61/122 | ETH2_MD2_N       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 18                                         |

| P62/124 | ETH2_MD2_P       |               |     | Connects to Ethernet-PHY AR8031 #2, pin 17                                         |

| P63/126 | GND              |               |     |                                                                                    |

| P64/128 | USB_O1_DN        | USB_OTG1_DN   | No  |                                                                                    |

| P65/130 | USB_O1_DP        | USB_OTG1_DP   | No  |                                                                                    |

| P66/132 | USB_O1_OTG_ID    | GPIO1_IO10    | Yes | Controlled by alternative pin function USB_OTG1_ID                                 |

| P67/134 | USB_O1_SSTXN     |               |     | USB OTG port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected.  |

| P68/136 | USB_O1_SSTXP     |               |     | USB OTG port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected.  |

| P69/138 | GND              |               |     |                                                                                    |

| P70/140 | USB_O1_SSRXN     |               |     | USB OTG port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected.  |

| P71/142 | USB_O1_SSRXP     |               |     | USB OTG port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected.  |

| P72/144 | USB_O1_VBUS      | USB_OTG1_VBUS | No  |                                                                                    |

| P73/146 | USB_O1_PWR_EN    | QSPI1A_DATA2  | Yes | Controlled by alternative pin function USB_OTG1_PWR                                |

| P74/148 | USB_O1_OC        | GPIO1_IO08    | Yes | Controlled by alternative pin function USB_OTG1_OC                                 |

| 150     | Non existing pin |               |     |                                                                                    |

| 152     | Non existing pin |               |     |                                                                                    |

| 154     | Non existing pin |               |     |                                                                                    |

| 156     | Non existing pin |               |     |                                                                                    |

| P75/158 | USB_H1_PWR_EN    | GPIO1_IO12    | Yes | Controlled by alternative pin function USB_OTG2_OC                                 |

| P76/160 | USB_H1_OC        | GPI01_I011    | Yes | Controlled by alternative pin function USB_OTG2_PWR                                |

| P77/162 | GND              |               |     |                                                                                    |

| P78/164 | USB_H1_DN        | USB_HOST_DN   | No  |                                                                                    |

| P79/166 | USB_H1_DP        | USB_HOST_DP   | No  |                                                                                    |

| P80/168 | USB_H1_SSTXN     |               |     | USB Host port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected. |

| P81/170 | USB_H1_SSTXP     |               |     | USB Host port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected. |

| P82/172  | GND                |               |     |                                                                                                                                                                            |

|----------|--------------------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P83/174  | USB_H1_SSRXN       |               |     | USB Host port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected.                                                                                         |

| P84/176  | USB_H1_SSRXP       |               |     | USB Host port #1 on iMX6SoloX does not support USB 3.0 so this pin is unconnected.                                                                                         |

| P85/178  | USB_H1_VBUS        | USB_HOST_VBUS | No  |                                                                                                                                                                            |

| P86/180  | USB_H2_PWR_EN      | SNVS_TAMPER   | No  | USB Host port #2 on iMX6SoloX does not exist.                                                                                                                              |

|          |                    |               |     | Non-standard pin allocation. Pin carry signal SNVS_TAMPER, iMX6SoloX ball V14.                                                                                             |

| P87/182  | USB_H2_OC          | ONOFF         | No  | USB Host port #2 on iMX6SoloX does not exist.                                                                                                                              |

|          |                    |               |     | Non-standard pin allocation. Pin carry signal ONOFF, iMX6SoloX ball W17                                                                                                    |

| P88/184  | GND                |               |     |                                                                                                                                                                            |

| P89/186  | USB_H2_DN          | KEY_COL0      | Yes | USB Host port #2 on iMX6SoloX does not exist.                                                                                                                              |

|          |                    |               |     | Non-standard pin allocation. KEY_COL0 signal, iMX6SoloX ball C23, During boot from eMMC, this pin carry signal SD3_CD_B. The signal has a 10K pulldown resistor to ground. |

|          |                    |               |     | Signal can be used if it does not interfere with booting (not driving the signal high before eMMC boot is complete).                                                       |

| P90/188  | USB_H2_DP          | CCM_CLK2      | No  | USB Host port #2 on iMX6SoloX does not exist.                                                                                                                              |

|          |                    |               |     | Non-standard pin allocation. Pin carry signal CCM_CLK2, iMX6SoloX ball W18                                                                                                 |

| P91/190  | GND                |               |     |                                                                                                                                                                            |

| P92/192  | COM board specific |               |     |                                                                                                                                                                            |

| P93/194  | COM board specific |               |     |                                                                                                                                                                            |

| P94/196  | COM board specific |               |     |                                                                                                                                                                            |

| P95/198  | COM board specific |               |     |                                                                                                                                                                            |

| P96/200  | COM board specific |               |     |                                                                                                                                                                            |

| P97/202  | COM board specific |               |     |                                                                                                                                                                            |

| P98/204  | COM board specific |               |     |                                                                                                                                                                            |

| P99/206  | COM board specific |               |     |                                                                                                                                                                            |

| P100/208 | COM board specific |               |     |                                                                                                                                                                            |

| P101/210 | COM board specific |               |     |                                                                                                                                                                            |

| P102/212 | COM board specific |               |     |                                                                                                                                                                            |

| P103/214 | COM board specific |               |     |                                                                                                                                                                            |

| P104/216 | COM board specific |               |     |                                                                                                                                                                            |

| P105/218 | COM board specific |               |     |                                                                                                                                                                            |

| P106/220 | COM board specific |               |     |                                                                                                                                                                            |

| P107/222 | COM board specific |               |     |                                                                                                                                                                            |

| P108/224 | COM board specific |               |     |                                                                                                                                                                            |

| P109/226 | COM board specific |               |     |                                                                                                                                                                            |

| P110/228 | COM board specific |               |     |                                                                                                                                                                            |

| P111/230 | COM board specific |               |     |                                                                                                                                                                            |

| P112/232 | COM board specific |               |     |                                                                                                                                                                            |

| P113/234 | COM board specific |               |     |                                                                                                                                                                            |

| P114/236 | COM board specific |              |     |                                                                                                                                                                                                                                           |

|----------|--------------------|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P115/238 | COM board specific |              |     |                                                                                                                                                                                                                                           |

| P116/240 | COM board specific |              |     |                                                                                                                                                                                                                                           |

| P117/242 | COM board specific |              |     |                                                                                                                                                                                                                                           |

| P118/244 | GND                |              |     |                                                                                                                                                                                                                                           |

| P119/246 | SPI-B_SSEL         | QSPI1B_SS0_B | Yes | Controlled by alternative pin function ECSPI3_SS0                                                                                                                                                                                         |

| P120/248 | SPI-B_MOSI         | QSPI1B_DATA0 | Yes | Controlled by alternative pin function ECSPI3_MOSI                                                                                                                                                                                        |

| P121/250 | SPI-B_MISO         | QSPI1B_DATA1 | Yes | Controlled by alternative pin function ECSPI3_MISO                                                                                                                                                                                        |

| P122/252 | SPI-B_CLK          | QSPI1B_SCLK  | Yes | Controlled by alternative pin function ECSPI3_SCLK                                                                                                                                                                                        |

| P123/254 | SPI-A_SSEL         | QSPI1A_SS0_B | Yes | Controlled by alternative pin function ECSPI1_SS0                                                                                                                                                                                         |

| P124/256 | SPI-A_MOSI         | QSPI1A_DATA0 | Yes | Controlled by alternative pin function ECSPI1_MOSI                                                                                                                                                                                        |

| P125/258 | SPI-A_MISO         | QSPI1A_DATA1 | Yes | Controlled by alternative pin function ECSPI1_MISO                                                                                                                                                                                        |

| P126/260 | SPI-A_CLK          | QSPI1A_SCLK  | Yes | Controlled by alternative pin function ECSPI1_SCLK                                                                                                                                                                                        |

| P127/262 | GND                |              |     |                                                                                                                                                                                                                                           |

| P128/264 | UART-C_RXD         | KEY_ROW3     | Yes | Controlled by alternative pin function UART5_RX_DATA                                                                                                                                                                                      |

| P129/266 | UART-C_TXD         | KEY_COL3     | Yes | Controlled by alternative pin function UART5_TX_DATA                                                                                                                                                                                      |

| P130/268 | UART-B_RXD         | SD1_DATA0    | Yes | Controlled by alternative pin function UART2_RX_DATA                                                                                                                                                                                      |

| P131/270 | UART-B_CTS         | SD1_DATA2    | Yes | Controlled by alternative pin function UART2_CTS_B                                                                                                                                                                                        |

| P132/272 | UART-B_RTS         | SD1_DATA3    | Yes | Controlled by alternative pin function UART2_RTS_B                                                                                                                                                                                        |

| P133/274 | UART-B_TXD         | SD1_DATA1    | Yes | Controlled by alternative pin function UART2_TX_DATA                                                                                                                                                                                      |

| P134/276 | UART-A_RXD         | GPIO1_IO05   | Yes | Controlled by alternative pin function UART1_RX_DATA                                                                                                                                                                                      |

| P135/278 | UART-A_CTS         | GPIO1_IO07   | Yes | Controlled by alternative pin function UART1_CTS_B                                                                                                                                                                                        |

| P136/280 | UART-A_RTS         | GPIO1_IO06   | Yes | Controlled by alternative pin function UART1_RTS_B                                                                                                                                                                                        |

| P137/282 | UART.A_TXD         | GPIO1_IO04   | Yes | Controlled by alternative pin function UART1_TX_DATA                                                                                                                                                                                      |

| P138/284 | PWM                | USB_H_STROBE | Yes | Controlled by alternative pin function PWM1_OUT. Pin can only be an output since signal pass through a voltage level translator.                                                                                                          |

| P139/286 | GPIO2              | SD1_CMD      | Yes | GPIO2 controlled by alternative pin function GPIO6_IO01                                                                                                                                                                                   |

| P140/288 | GPIO1              | SD1_CLK      | Yes | GPIO1 controlled by alternative pin function GPIO6_IO00                                                                                                                                                                                   |

| P141/290 | PERI_PWR_EN        | GPIO4_IO26   | Yes | Enable signal (active high) for carrier board peripheral power supplies. More information about carrier board design can be found in EA COM Board specification.                                                                          |

| P142/292 | RESET_IN           |              |     | Reset input, active low. Pull signal low to activate reset. No need to pull signal high externally.                                                                                                                                       |

| P143/294 | RESET_OUT          |              |     | Reset (open drain) output, active low. Driven low during reset.  1.5K pull-up resistor to VIN.                                                                                                                                            |

| P144/296 | GND                |              |     |                                                                                                                                                                                                                                           |

| P145/298 | VBAT               |              |     | Supply voltage from coin cell battery for keeping PMIC and RTC functioning during standby.                                                                                                                                                |

| P146/300 | E2PROM_WP          |              |     | Should be left open (will write protect the on-board parameter storage E2PROM), or connected to GND (will enable writes to the on-board parameter storage E2PROM AND place the i.MX 6SoloX SoC in USB OTG boot mode after a power cycle). |

| P147/302 | VIN                |              |     | Main input voltage supply (3.3V)                                                                                                                                                                                                          |

| P148/304 | VIN                |              |     | Main input voltage supply (3.3V)                                                                                                                                                                                                          |

| P149/306 | VIN                |              |     | Main input voltage supply (3.3V)                                                                                                                                                                                                          |

| P150/308 | VIN | Main input voltage supply (3.3V) |

|----------|-----|----------------------------------|

| P151/310 | VIN | Main input voltage supply (3.3V) |

| P152/312 | VIN | Main input voltage supply (3.3V) |

| P153/314 | VIN | Main input voltage supply (3.3V) |

| P154/316 | VIN | Main input voltage supply (3.3V) |

| P155/318 | VIN | Main input voltage supply (3.3V) |

| P156/320 | VIN | Main input voltage supply (3.3V) |

The table below lists the bottom side pins, S1-S158, even numbers.

|                              |             | · .                      |                            |                                                                                                                          |

|------------------------------|-------------|--------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Bottom<br>Side Pin<br>Number | EACOM Board | i.MX 6SoloX Ball<br>Name | Alternative pin functions? | Notes                                                                                                                    |

| S1/1                         | MQS_RIGHT   | CSI_VSYNC                | Yes                        | Signal also available on pin S115/235. Both interfaces cannot be active simultaneous.                                    |

| S2/3                         | MQS_LEFT    | CSI_HSYNC                | Yes                        | Signal also available on pin S114/233. Both interfaces cannot be active simultaneous.                                    |

| S3/5                         | GND         |                          |                            |                                                                                                                          |

| S4/7                         | AUDIO_TXFS  | CSI_DATA01               | Yes                        | ESAI, AUD6 or SAI1 interface. Note that CSI_DATA01 is also available on pin S120/245.                                    |

| S5/9                         | AUDIO_RXD   | CSI_VSYNC                | Yes                        | ESAI, AUD6 or SAI1 interface. Note that CSI_VSYNC is also available on pin S115/235.                                     |

| S6/11                        | AUDIO_TXC   | CSI_DATA00               | Yes                        | ESAI, AUD6 or SAI1 interface. Note that CSI_DATA00 is also available on pin S119/243.                                    |

| S7/13                        | AUDIO_TXD   | CSI_HSYNC                | Yes                        | ESAI, AUD6 or SAI1 interface. Note that CSI_HSYNC is also available on pin S114/233.                                     |

| S8/15                        | AUDIO_MCLK  | CSI_PIXCLK               | Yes                        | ESAI, AUD6 or SAI1 interface Alternative function AUDIO_CLK_OUT. Note that CSI_PIXCLK is also available on pin S117/239. |

| S9/17                        | GND         |                          |                            |                                                                                                                          |

| S10/19                       | SPDIF_IN    | ENET2_COL                | Yes                        | Controlled by alternative pin function SPDIF_IN                                                                          |

| S11/21                       | SPDIF_OUT   | ENET1_RX_CLK             | Yes                        | Controlled by alternative pin function SPDIF_OUT                                                                         |

| S12/23                       | CAN2_TX     | QSPI1A_DQS               | Yes                        | Controlled by alternative pin function CAN2_TX                                                                           |

| S13/25                       | CAN2_RX     | QSPI1B_SS1_B             | Yes                        | Controlled by alternative pin function CAN2_RX                                                                           |

| S14/27                       | CAN1_TX     | QSPI1B_DQS               | Yes                        | Controlled by alternative pin function CAN1_TX                                                                           |

| S15/29                       | CAN1_RX     | QSPI1A_SS1_B             | Yes                        | Controlled by alternative pin function CAN1_RX                                                                           |

| S16/31                       | GND         |                          |                            |                                                                                                                          |

| S17/33                       | LVDS1_D3_P  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S18/35                       | LVDS1_D3_N  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S19/37                       | GPIO        |                          |                            |                                                                                                                          |

| S20/39                       | LVDS1_D2_P  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S21/41                       | LVDS1_D2_N  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S22/43                       | GND         |                          |                            |                                                                                                                          |

| S23/45                       | LVDS1_D1_P  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S24/47                       | LVDS1_D1_N  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S25/49                       | GND         |                          |                            |                                                                                                                          |

| S26/51                       | LVDS1_D0_P  |                          |                            | LVDS interface #1 not assigned on this COM board.                                                                        |

| S27/53  | LVDS1_D0_N     |              |     | LVDS interface #1 not assigned on this COM board.                                                                                       |

|---------|----------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| S28/55  | GND            |              |     |                                                                                                                                         |

| S29/57  | LVDS1_CLK_P    |              |     | LVDS interface #1 not assigned on this COM board.                                                                                       |

| S30/59  | LVDS1_CLK_N    |              |     | LVDS interface #1 not assigned on this COM board.                                                                                       |

| S31/61  | GND            |              |     |                                                                                                                                         |

| S32/63  | LVDS0_D3_P     | LVDS_DATA3_P | No  |                                                                                                                                         |

| S33/65  | LVDS0_D3_N     | LVDS_DATA3_N | No  |                                                                                                                                         |

| S34/67  | GPIO           |              |     |                                                                                                                                         |

| S35/69  | LVDS0_D2_P     | LVDS_DATA2_P | No  |                                                                                                                                         |

| S36/71  | LVDS0_D2_N     | LVDS_DATA2_N | No  |                                                                                                                                         |

| S37/73  | GND            |              |     |                                                                                                                                         |

| S38/75  | LVDS0_D1_P     | LVDS_DATA1_P | No  |                                                                                                                                         |

| S39/77  | LVDS0_D1_N     | LVDS_DATA1_N | No  |                                                                                                                                         |

| S40/79  | GND            |              |     |                                                                                                                                         |

| S41/81  | LVDS0_D0_P     | LVDS_DATA0_P | No  |                                                                                                                                         |

| S42/83  | LVDS0_D0_N     | LVDS_DATA0_N | No  |                                                                                                                                         |

| S43/85  | GND            |              |     |                                                                                                                                         |

| S44/87  | LVDS0_CLK_P    | LVDS_CLK_P   | No  |                                                                                                                                         |

| S45/89  | LVDS0_CLK_N    | LVDS_CLK_N   | No  |                                                                                                                                         |

| S46/91  | I2C-A_SDA      | GPI01_I001   | Yes | Controlled by alternative pin function I2C1_SDA                                                                                         |

| S47/93  | I2C-A_SCL      | GPIO1_IO00   | Yes | Controlled by alternative pin function I2C1_SCL                                                                                         |

| S48/95  | I2C-B_SDA      | GPIO1_IO03   | Yes | Controlled by alternative pin function I2C2_SDA                                                                                         |

| S49/97  | I2C-B_SCL      | GPIO1_IO02   | Yes | Controlled by alternative pin function I2C2_SCL                                                                                         |

| S50/99  | HDMI/I2C-C_SDA | KEY_ROW4     | Yes | Controlled by alternative pin function I2C3_SDA                                                                                         |

| S51/101 | HDMI/I2C-C_SCL | KEY_COL4     | Yes | Controlled by alternative pin function I2C3_SCL                                                                                         |

| S52/103 | TP_RST         | QSPI1A_DATA3 | Yes | Controlled by alternative pin function GPIO4_IO19                                                                                       |

| S53/105 | TP_IRQ         | KEY_ROW0     | Yes | Controlled by alternative pin function GPIO2_IO15                                                                                       |

| S54/107 | DISP_PWR_EN    | ENET1_CRS    | Yes | Controlled by alternative pin function GPIO2_IO01                                                                                       |

| S55/109 | BL_PWR_EN      | GPI01_I009   | Yes | Controlled by alternative pin function GPIO4_IO18                                                                                       |

| S56/111 | BL_PWM         | USB_H_DATA   | Yes | Controlled by alternative pin function PWM2_OUT. Signal can <b>only be output</b> since signal pass through a voltage level translator. |

| S57/113 | GND            |              |     |                                                                                                                                         |

| S58/115 | LCD_R0         | LCD1_DATA16  | Yes |                                                                                                                                         |

| S59/117 | LCD_R1         | LCD1_DATA17  | Yes |                                                                                                                                         |

| S60/119 | LCD_R2         | LCD1_DATA18  | Yes |                                                                                                                                         |

| S61/121 | LCD_R3         | LCD1_DATA19  | Yes |                                                                                                                                         |

| S62/123 | LCD_R4         | LCD1_DATA20  | Yes |                                                                                                                                         |

| S63/125 | LCD_R5         | LCD1_DATA21  | Yes |                                                                                                                                         |

| S64/127 | LCD_R6         | LCD1_DATA22  | Yes |                                                                                                                                         |

| S65/129 | LCD_R7         | LCD1_DATA23  | Yes |                                                                                                                                         |

| S66/131 | LCD_G0         | LCD1_DATA08  | Yes |                                                                                                                                         |

| S67/133 | LCD_G1         | LCD1_DATA09  | Yes |                                                                                                                                         |

| S68/135  | LCD_G2                  | LCD1_DATA10        | Yes |                                                                                                       |

|----------|-------------------------|--------------------|-----|-------------------------------------------------------------------------------------------------------|

| S69/137  | LCD_G3                  | LCD1_DATA11        | Yes |                                                                                                       |

| S70/139  | LCD_G4                  | LCD1_DATA12        | Yes |                                                                                                       |

| S71/141  | LCD_G5                  | LCD1_DATA13        | Yes |                                                                                                       |

| S72/143  | LCD_G6                  | LCD1_DATA14        | Yes |                                                                                                       |

| S73/145  | LCD_G7                  | LCD1_DATA15        | Yes |                                                                                                       |

| S74/147  | GND                     |                    |     |                                                                                                       |

| S75/149  | LCD_B0                  | LCD1_DATA00        | Yes |                                                                                                       |

| 151      | Non existing pin        |                    |     |                                                                                                       |

| 153      | Non existing pin        |                    |     |                                                                                                       |

| 155      | Non existing pin        |                    |     |                                                                                                       |