Открой для себя XILINX: отладочная плата Open3S250E Package A

Open3S250E Package A – отладочная плата, разработанная дляXilinx FPGA ПЛИС серии Spartan-3E XC3S250E. На плате имеется широкий набор стандартных интерфейсов для различных модулей расширения. Отладочная плата состоит из материнской платы DVK601 и модуля ПЛИС Core3S250E. Модульность и открытый дизайн делают Open3S250E Package A идеальным средством для начала разработки приложений на основе ПЛИС Xilinx семейства Spartan-3E.

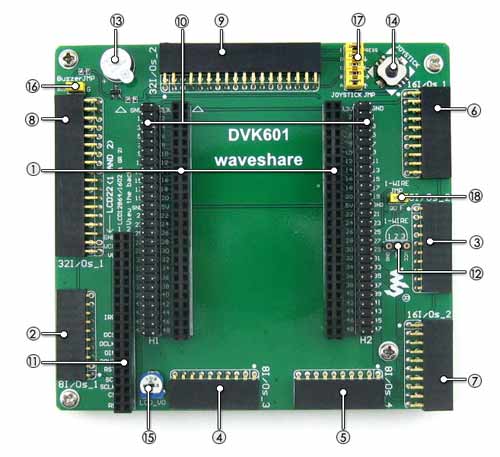

Рис. 1. Материнская плата DVK601 отладочного средства Open3S250E Package A

Отличительные особенности:

- Материнская плата DVK601:

- разъем для подключения модуля FPGA (CPLD) ПЛИС,

- 8I/O_1 интерфейс для подключения модулей расширения,

- 8I/O_2 интерфейс для подключения модулей расширения,

- 8I/O_3 интерфейс для подключения модулей расширения,

- 8I/O_4 интерфейс для подключения модулей расширения,

- 16I/O_1 интерфейс для подключения модулей расширения,

- 16I/O_2 интерфейс для подключения модулей расширения,

- 32I/O_1 интерфейс для подключения модулей расширения,

- 32 I/O_2 интерфейс для подключения модулей расширения.

Указанные выше I/O интерфейсы могут быть настроены как USART, I2C, SPI, PS/2 и др. и управлять такими устройствами, как FRAM, FLASH, USB, Ethernet и т.д. - разъем расширения FPGA:

- выводы ПЛИС доступны на разъеме,

- возможно подключение платы расширения SDRAM;

- Интерфейс LCD для подключения ЖКИ LCD22, LCD12864, LCD1602;

- Интерфейс 1-Wire для подключения изделий в корпусе TO-92, например, температурный датчик DS18B20 и др.;

- Зуммер;

- Пятипозиционный джойстик;

- Потенциометр для регулировки задней подсветки LCD22 или контрастности LCD12864, LCD1602;

- Джампер зуммера;

- Джампер джойстика;

- Джампер интерфейса 1-Wire.

Для джамперов 16-18:

Джамперы устанавливаются для использования с демонстрационными программами; для коммутации Open3S250E Package A с выводами платы пользователя джамперы должны быть сняты.

DVK601 поддерживает широкий набор мезонинных модулей, однако для некоторых модулей ряд интерфейсов может оказаться не подключенным, что необходимо учитывать в работе.

- Модуль Core3S250E

Рис. 2 Модуль ПЛИС Core3S250E

- XC3S250E: XILINX Spartan-3E FPGA:

- рабочая частота: 50MHz,

- рабочее напряжение: 1.15 V?3.3 V,

- корпус: QFP144,

- количество I/O: 80,

- LEs: 250K,

- RAM: 216kb,

- DCMs: 4,

- отладка/ программирование: поддержка JTAG;

- Стабилизатор напряжения AMS1117-3.3, 3.3 V;

- Стабилизатор напряжения AMS1117-2.5, 2.5 V;

- Стабилизатор напряжения AMS1117-1.2, 1.2 V;

- CF02S - последовательная FLASH память для хранения кодов;

- Индикатор питания;

- Светодиоды;

- Индикатор инициализации FPGA;

- Кнопка Сброса;

- Кнопка nCONFIG: для повторного конфигурирования микросхемы FPGA, эквивалент сброса питания;

- Выключатель питания;

- Кварцевый генератор 50 M;

- Разъем 5 V DC;

- JTAG интерфейс: для отладки/ программирования;

- Выводы расширения FPGA, VCC, GNDи всех портов I/O;

- Джамперы светодиодов.

- XC3S250E: XILINX Spartan-3E FPGA:

Отладочная плата Open3S250E Package A поставляется с различными демонстрационными примерами (Таблица 1) для периферии и позволяет пользователю быстро начать разработку собственного приложения.

Таблица 1

| Peripheral | Description | Interface | Verilog | VHDL |

| AT24CXX | EEPROM | I2C | Y | Y |

| FM24CXX | FRAM | I2C | Y | Y |

| AT45DBXX | DATAFLASH | SPI | Y |

|

| PCF8563 | RTC | I2C | Y |

|

| PCF8591 | 4xAD, 1xDA | I2C | Y |

|

| DS18B20 | Temperature sensor | 1-WIRE | Y |

|

| SP3232 | Serial communication | UART | Y | Y |

| SP3485 | Serial communication | UART | Y | Y |

| PL2303 | USB TO UART | UART | Y | Y |

| CY7C68013A | USB DEVICE | I/Os |

| Y |

| Buzzer | Sound device | 1I/O (PWM) | Y | Y |

| PS/2 keyboard | Input device | PS/2 | Y | Y |

| Single buttons | Input device | ---- | Y | Y |

| 4x4 keypad | Input device | 8I/Os | Y | Y |

| Joystick | Input device | 5I/Os | Y | Y |

| LED | Display device | ---- | Y | Y |

| 8 SEG LED | Display device | 13I/Os | Y | Y |

| VGA monitor | Display device | VGA | Y | Y |

| Character LCD | Display device | 11I/Os | Y | Y |

| Graphic LCD | Display device | 11I/Os | Y | Y |

Для программирования и отладки на плату интегрирован интерфейс JTAG (Таблица 2).

Таблица 2

| Pin | Signal Name | Description |

| 1 | GND | Signal ground |

| 2 | VCC(TRGT) | Target power supply |

| 3 | GND | Signal ground |

| 4 | TMS | JTAG state machine control |

| 5 | GND | Signal ground |

| 6 | TCK | Clock signal |

| 7 | GND | Signal ground |

| 8 | TDO | Data from device |

| 9 | GND | Signal ground |

| 10 | TDI | Data to device |

| 11 | GND | Signal ground |

| 12 | NC |

|

| 13 | GND | Signal ground |

| 14 | NC |

|

| 15 | GND | Signal ground |

Рис. 3. Разъем интерфейса JTAG отладочной платы Open3S250E Package A

Open3S250E Package A поставляется с CD диском, на котором имеются:

- User Guide

- Среда разработки Xilinx ISE 12

- Демокоды (Verilog, VHDL)

- Схема в формате pdf

- Документация для разработчика

Комплектация:

- Open3S250E development board x 1;

- 4-pin wire x 2;

- 2-pin wire x 2;

- USB кабель питания x 1;

- User guide CD x 1.

Анонс составил и подготовил

Шрага Александр,

office@terraelectronica.ru

Производители: Wvshare

Разделы: Аксессуары для микроконтроллерных плат

Опубликовано: 18.12.2015

_500.jpeg)