Руководство по электромагнитной совместимости в DC-DC-преобразователях. Часть 6: борьба с помехами в DC/DC-преобразователях с дискретными МОП-транзисторами

Первые пять частей данного руководства были посвящены рассмотрению практических методов борьбы с кондуктивным и радиочастотными помехами [1-5]. В предыдущей статье отдельно рассматривались рекомендации по борьбе с помехами в регуляторах, построенных на базе интегральных DC/DC-преобразователей со встроенными МОП-транзисторами [5]. В данной статье исследуются способы борьбы с электромагнитными помехами в преобразователях с дискретными МОП-транзисторами.

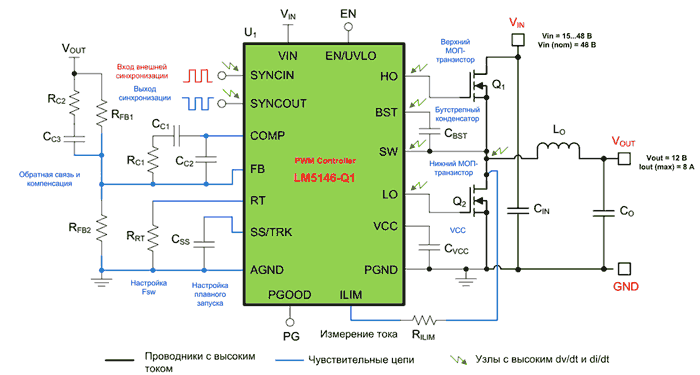

Пример синхронного понижающего DC/DC-преобразователя с дискретными МОП-транзисторами представлен на рис. 1. DC/DC-преобразователи с дискретными МОП-транзисторами имеют множество преимуществ. Среди их достоинств можно отметить: высокие значения нагрузочных токов, улучшенные тепловые характеристики, высокую гибкость при выборе компонентов и специальных функций. Однако с точки зрения электромагнитной совместимости проектирование таких DC/DC-преобразователей оказывается значительно сложнее, чем создание схем с интегральными DC/DC-преобразователями со встроенными силовыми ключами.

Рис. 1. Схема синхронного понижающего преобразователя, в которой DC/DC-контроллер управляет силовыми МОП-транзисторами Q1 и Q2

При создании преобразователей с дискретными МОП-транзисторами следует учитывать две особенности. Во-первых, печатная плата, содержащая дискретные силовые ключи и управляющий DC/DC-контроллер, по определению не может быть такой же компактной, как плата преобразователя, построенного на базе интегральной микросхемы с оптимизированным расположением выводов и со встроенными ключами и драйверами [5]. Во-вторых, в интегральных преобразователях управление мертвым временем обычно оказывается более точным, так как время переключения МОП-транзисторов хорошо известно. В результате длительность фазы проводимости встроенного диода максимально сокращается, что с одной стороны приводит к уменьшению потерь, а с другой стороны снижает уровень помех, являющихся следствием обратного восстановления диода.

В этой статье будут предложены советы и рекомендации по компоновке и трассировке многослойной печатной платы для DC/DC-преобразователей с дискретными МОП-транзисторами. Эти рекомендации позволяют существенно снизить уровень генерируемых помех. Необходимым условием достижения низкого уровня шумов является минимизация паразитных индуктивностей наиболее критичных контуров за счет тщательного выбора компонентов силового каскада и правильной разводки печатной плат. Также в статье разбирается пример трассировки, который наглядно демонстрирует, что добиться уменьшения кондуктивных помех можно, не жертвуя эффективностью преобразователя или его тепловыми характеристиками.

Анализ существующих проблем с электромагнитной совместимостью

Проблемы с электромагнитной совместимости (ЭМС) возникают только при одновременном наличии трех составляющих: источника шума, канала связи и приемника помех (жертвы). Таким образом, воздействуя на эти компоненты, можно добиться требуемых показателей ЭМС. Обычно на практике применяется комплексный подход, который подразумевает использование нескольких методов борьбы с помехами, в том числе устранение индуктивной или емкостной связи между источником и приемником, а также защиту чувствительного устройства от кондуктивных помех с помощью фильтров и от радиочастотных помех с помощью экранирования [4].

С низкочастотными помехами, являющимися следствием прерывистого характера входных и выходных токов преобразователя, можно относительно легко справиться с помощью обычных НЧ-фильтров. Гораздо больше проблем создают гармонические составляющие, возникающие из-за высоких скоростей переключения dv/ dt и di/ dt.

Микросхемы DC/DC-контроллеров с рабочими напряжениями до 100 В, как правило, имеют интегрированные драйверы силовых ключей. Эти драйверы способны обеспечивать высокую скорость переобучений силовых МОП-транзисторов. Например, для кремниевых транзисторов типовые скорости нарастания сигналов превышают 10 В/нс и 1 А/нс, при этом для нитрид-галлиевых ключей (GaN) скорости нарастания оказываются еще выше. Во второй части данного руководство подробно рассматривалась связь между временными характеристиками трапецеидального сигнала и его частотным спектром, при этом было показано, что скорость нарастания напрямую определяет частотные составляющие спектра [2]. В той же статье предлагались методы снижения dv/dt и di/dt, позволяющие уменьшить уровень генерируемых помех.

В дополнение к проблемам, вызванным резкими перепадами напряжений и токов, возникают проблемы, связанные с перенапряжениями и ВЧ-колебаниями (звонами), появляющимися в процессе коммутаций. На рис. 2 показана осциллограмма напряжения на выходе силового каскада синхронного преобразователя с жесткими переключениями. Частота звона лежит в диапазоне от 50 МГц до 250 МГц и зависит от резонансной частоты паразитного LC-контура, образованного паразитной индуктивностью силового каскада (LLOOP) и выходной емкостью МОП-транзистора (COSS).

Эти высокочастотные составляющие способны распространяться посредством паразитных связей и без проблем проникать на входные и выходные шины, а также воздействовать на расположенные поблизости цепи и компоненты. К сожалению, с такими помехами сложно бороться с помощью обычных методов фильтрации. Восстановление встроенных обратных диодов МОП-транзисторов вызывает аналогичные отрицательные эффекты, которые вносят свой вклад в звон при протекании тока восстановления в паразитной индуктивности контура.

Рис. 2. Эквивалентные схемы понижающего преобразователя при различных состояниях транзистора Q1 и форма напряжения на выходе силового каскада преобразователя (узел SW)

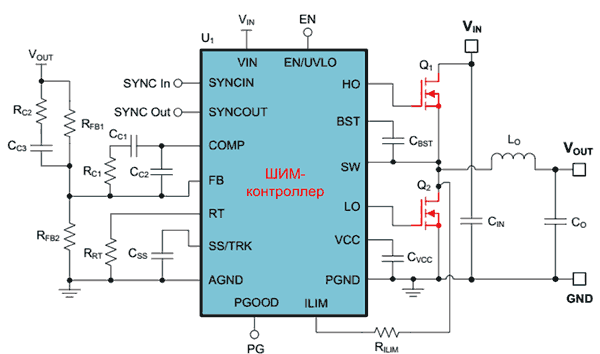

Схема, представленная на рис. 3, определяет наиболее критичные силовые контуры понижающего преобразователя [6]. Эти контуры содержат компоненты, связанные с формированием сигналов с высокой скоростью нарастания. Аналогичные контуры можно выделить и в схемах других типов преобразователей: повышающем, инвертирующем повышающе-понижающем, SEPIC и др. Уменьшение площади силового контура имеет важное значение, так как приводит к пропорциональному уменьшению паразитной индуктивности и связанного с ней магнитного поля. [3].

Рис. 3. Упрощенная схема синхронного понижающего преобразователя с указанием наиболее критичных контуров с повышенным риском генерации электромагнитных помех

При проектировании DC/DC-преобразователей одной из важнейших задач становится максимальное увеличение частоты резонанса паразитного LC-контура за счет снижения паразитной индуктивности. Уменьшение паразитной индуктивности позволяет сократить объем накапливаемой реактивной энергии, а также ограничить выбросы напряжения при коммутациях. Кроме того, чем выше частота звона, тем меньше может быть сопротивление контура для обеспечения аналогичного коэффициента затухания колебаний. Не стоит забывать и о том, что скин-эффект на высоких частотах дополнительно увеличивает паразитное сопротивление контура.

На рис. 3 также показаны пути протекания затворных токов при включении и выключении МОП-транзисторов нижнего и верхнего плеча. Далее будут предложены советы и рекомендации по трассировке печатной платы DC/DC-преобразователя с дискретными МОП-транзисторами. Выполнение этих рекомендация гарантирует достижение минимальных паразитных индуктивностей силового контура и цепей управления [3].

Рекомендации по трассировке печатной платы для достижения минимального уровня помех

В этом разделе представлены основные советы и рекомендаций по размещению компонентов и трассировке печатной платы для DC/DC-преобразователей с дискретными МОП-транзисторами. Некоторые из этих рекомендаций совпадают с рекомендациями, которые были предложены в предыдущей части данного руководства и относились к трассировке интегральных DC/DC-преобразователей со встроенными МОП-транзисторами [5]. Далее в статье рассматривается конкретный пример компоновки печатной платы понижающего преобразователя с оптимизированной электромагнитной совместимостью.

- Трассировка и размещение компонентов

- Разводку всех компонентов, относящихся к силовому контуру, необходимо выполнять на верхнем слое печатной платы. Избегайте размещения дросселя на нижней стороне платы, где он может излучать помехи в сторону пластины заземления испытательной установки.

- Размещайте развязывающие конденсаторы в непосредственной близости от выводов VCC, VDD и BIAS. Убедитесь, что цепь AGND на печатной плате сначала подключается к конденсаторам CVCC и CBIAS, и только от них идет соединение с общей землей GND.

- Располагайте бутстрепный конденсатор СBOOT максимально близко к узлам BOOT и SW. Бутстрепный конденсатор CBOOT и силовой контур следует разделить с помощью полигона или трассы земли GND, чтобы минимизировать уровень синфазных помех.

- Организация заземления

- Располагайте плоскость земли на втором слое печатной платы, как можно ближе к верхнему сигнальному слою. Это обеспечит подавление магнитного поля, снижение паразитной индуктивности и защиту от шума.

- Используйте минимальную толщину препрега между верхним сигнальным слоем и слоем земли. В требованиях к конструкции печатной платы укажите расстояние 6 милов (0,15 мм).

- Входные и выходные конденсаторы

- Размещайте входной конденсатор CIN таким образом, чтобы минимизировать площадь петли, образованной конденсатором CIN и верхним МОП-транзистором. Аналогичной рекомендации необходимо следовать при размещении выходных конденсаторов COUT при компоновке повышающих или SEPIC-регуляторов. В зависимости от расположения конденсаторов относительно МОП-транзистора силовой контур может иметь плоскую или вертикальную ориентацию [6].

- Для подключения входных и выходных конденсаторов (CIN и COUT) к земле необходимо использовать локализованный полигон на верхней стороне платы, который в свою очередь следует подключать к внутреннему слою (или слоям) земли с помощью нескольких переходных отверстий.

- Размещайте керамические конденсаторы типоразмеров 0402 или 0603 с низкой эквивалентной последовательной индуктивностью (ESL) в непосредственной близости от силовых МОП-транзисторов, чтобы минимизировать паразитную индуктивность контура.

- Трассировка цепей дросселя

- Располагайте дроссель максимально близко к МОП-транзисторам. Постарайтесь обеспечить минимальную площадь полигона, подключенного к выходу силового каскада, чтобы уменьшить влияние емкостной связи и синфазных токов. В идеале большая часть полигона должна быть занята контактной площадкой дросселя и контактными площадками транзисторов.

- Используйте полигоны земли и переходные отверстия (подключенные к земле), для экранирования силового контура преобразователя.

- Уделите внимание конструкции индуктивности. Проверьте, что конец обмотки, подключенной к узлу SW, находится на нижнем слое обмотки и сверху экранирован и закрыт витками, подключенными к выходу VOUT (в случае понижающего преобразователя) или ко входу VIN (в случае повышающего преобразователя).

- Используйте катушки индуктивности с нижним расположением выводов. Избегайте дросселей с большими боковыми выводами, так как они могут выступать в качестве излучающей антенны.

- Если возможно, то используйте экранированную индуктивность. Подключайте клеммы экрана к слою земли.

- Трассировка затворных цепей управления МОП-транзисторами

Разместите микросхему DC/DC-контроллера как можно ближе к силовым МОП-транзисторам, выполнив следующие шаги:

- Выполните трассировку проводников управляющих цепей HO и SW в виде дифференциальной линии. Чтобы обеспечить минимальную длину проводников и минимальную площадь образованного ими контура, подключите эти линии напрямую к выводам МОП-транзистора.

- Соедините вывод LO и нижний МОП-транзистор по кратчайшему пути. Проводник должен располагаться максимально близко к слою земли, поэтому, как уже говорилось выше, используйте минимальную толщину препрега между верхним сигнальным слоем и внутренним слоем земли.

- Минимизируйте паразитную связь между силовым контуром и контурами управления. Для этого выполняйте взаимную трассировку проводников под прямым углом [6].

- Размещение защитных компонентов и фильтров

- Располагайте компоненты фильтра вдали от силового контура и дросселя. Если не удается разместить фильтр достаточно далеко, то следует переместить его на обратную сторону печатной платы.

- Чтобы минимизировать емкостную связь, влияющую на коэффициент затухания фильтра, необходимо сделать вырезы на всех слоях непосредственно под фильтром.

- Как пояснялось в пятой части данного руководства, чтобы снизить скорость нарастания напряжения в силовом контуре, ограничить выбросы и звоны, необходимо замедлить включение МОП-транзистора. Для этого необходим резистор (желательно не более 10 Ом), включенный последовательно с CBOOT. Для достижения повышенной эффективности следует рассмотреть возможность использования контроллера с отдельными выводами для включения и выключения силового транзистора.

- Если принято решение использовать помехоподавляющие цепи, то следует обеспечить наименьшую площадь контура для протекания шумовых токов. Рекомендуется, в первую очередь, подключать к выходу силового каскада (узел SW) компонент с минимальными габаритами (обычно это конденсатор).

- Используйте четырехслойную печатную плату с внутренним слоем земли, чтобы добиться значительного улучшения характеристик ЭМС по сравнению с двухслойной печатной платой. Избегайте значительных неоднородностей и межслойных переходов при разводке контуров высокочастотных токов вблизи силовых транзисторов.

- Рассмотрите возможность использования металлического корпуса для экранирования радиочастотных помех. Экран должен закрывать все элементы преобразователя, кроме фильтра. По сути, при подключении металлического корпуса к земле, он образует клетку Фарадея со слоем земли на печатной плате.

Пример трассировки синхронного DC/DC-преобразователя с дискретными МОП-транзисторами

На рис. 4 показана схема синхронного понижающего преобразователя, предназначенного для малошумящих автомобильных или промышленных приложений. Микросхема контроллера имеет несколько особенностей, способствующих улучшению ЭМС-характеристик. Например, она обеспечивает постоянную частоту коммутации силовых транзисторов, позволяет использовать внешнюю синхронизацию и управлять скоростью включения верхнего МОП-транзистора [7].

Рис. 4. Схема понижающего преобразователя с указанием узлов и проводников наиболее критичных с точки зрения трассировки печатной платы

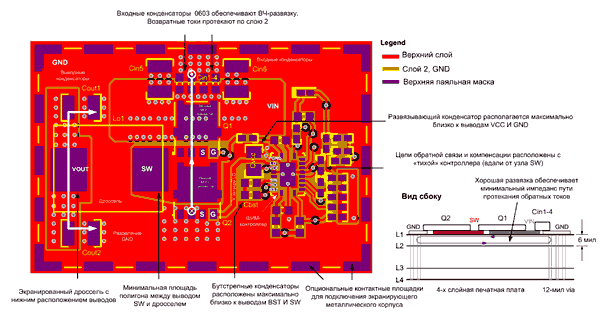

На рис. 5 показано два варианта компоновки МОП-транзисторов и входных конденсаторов, которые образуют плоский силовой контур (отмечен белыми стрелками). Все проводники этого контура располагаются на верхнем слое печатной платы, в то время как контроллер расположен на нижней стороне платы. Токи, протекающие в контуре, отображаются на слое земли в виде возвратных токов, что обеспечивает минимальную паразитную индуктивность.

На рис. 5b представлен улучшенный вариант размещения компонентов. В данном случае полевой транзистор (Q1) повернут на 90 градусов. С одной стороны, это улучшает отвод тепла от Q1, а с другой стороны, позволяет разместить конденсатор Cin1 типоразмера 0603 с малой паразитной индуктивностью максимально близко к МОП-транзистору, что повышает качество высокочастотной развязки. П-образное размещение элементов обеспечивает минимальную длину контура, образованного выходными конденсаторами и нижним МОП-транзистором.

Рис. 5. Два варианта компоновки печатной платы с плоской ориентацией силового контура

Оптимизированный вариант трассировки печатной платы

На рис. 6 показан улучшенный вариант трассировки печатной платы DC/DC-преобразователя с дискретными МОП-транзисторами. Основные достоинства этого варианта определяются уменьшенной площадью силового контура и правильной компоновкой печатной платы. Второй слой печатной платы, как и в предыдущем варианте, используется для локализации возвратных токов силового контура, однако возвратная часть контура лежит непосредственно под частью контура на верхнем слое. Таким образом, силовой контур имеет уже не плоскую, а вертикальную ориентацию [7,8,9], а общая площадь контура оказывается минимальной. Токи, протекая в противоположных направлениях на верхнем слое и слое 2, обеспечивают самоподавление поля, что дополнительно уменьшает паразитную индуктивность. На рис. 6 также представлено изображение бокового разреза печатной платы, поясняющее концепцию создания вертикального контура в структуре многослойной печатной платы.

Четыре входных конденсатора (CIN1 … CIN4) с малыми типоразмерами 0402 или 0603 и низкой паразитной индуктивностью, располагаются между двумя большими конденсаторами CIN5 и CIN6 в максимальной близости от верхнего МОП-транзистора (рис. 6). Подключение этих конденсаторов к земляному слою (слой 2) выполнено с помощью нескольких переходных отверстий диаметром 12 милов (0,3 мм). Земляная плоскость слоя 2 обеспечивает прямой путь возвратных токов непосредственно под транзисторами к истоку нижнего МОП-транзистора.

Полигон SW (выход силового контура) имеет минимальную площадь. Большая его часть приходится на контактную площадку дросселя и контактные площадки МОП-транзисторов. Этот полигон дополнительно экранируется с помощью внешнего полигона земли. Трассировка цепей SW и BST целиком выполнена на верхнем слое, поэтому переходные отверстия отсутствуют, и сигналы с большой скоростью нарастания dv/ dt не появляются на нижней стороне печатной платы. Это позволяет избежать емкостной связи с пластиной заземления при выполнении испытаний на электромагнитную совместимость.

Наконец, размещение двух выходных керамических конденсаторов, COUT1 и COUT2, с двух сторон от катушки индуктивности разделяет выходной контур на два подконтура. Наличие двух контуров с противоположными направлениями протекания токов помогает смягчить эффект «отскока от земли».

Рис. 6. Оптимизированный вариант трассировки с вертикальной ориентацией силового контура

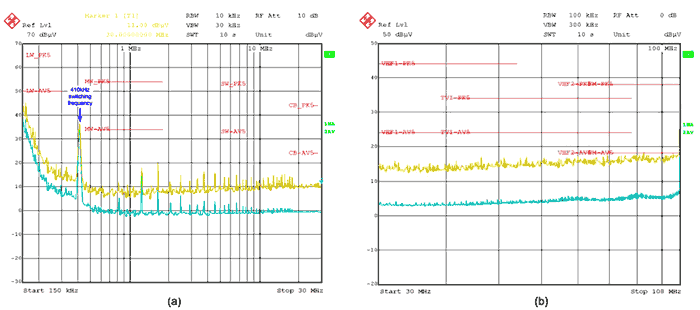

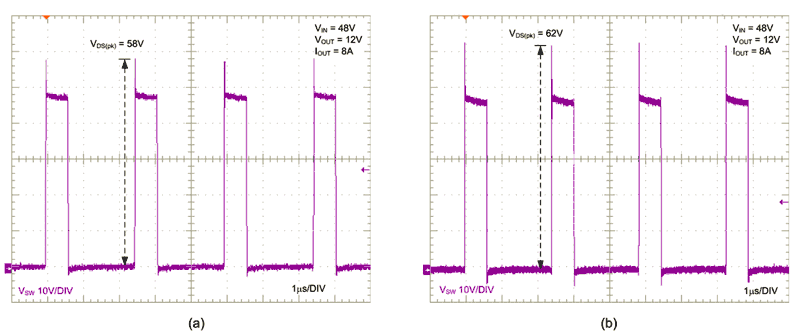

На рис. 7а показана осциллограмма напряжения на выходе силового каскада DC/DC-преобразователя с оптимизированной компоновкой печатной платы (рис. 6). Схема преобразователя представлена на рис. 4. На осциллограмме не видно ярко выраженного звона при переключениях. Амплитуда перенапряжений при выключении достаточно мала, а отрицательный выброс при включении практически отсутствует. Все это обеспечивает минимальный уровень шумов в диапазоне от 50 МГц. Для сравнения, на рис. 7b показана осциллограмма того же преобразователя, но с платой, изображенной на рис. 5b. Не сложно заметить, что выброс напряжения при выключении оказывается меньше примерно на 4 В.

Рис. 7. Сравнение осциллограмм напряжения на выходе силового каскада DC/DC-преобразователя при VIN = 48 В и IOUT = 8 А: оптимизированная трассировка с вертикальной ориентацией силового контура (a); трассировка с плоской ориентацией силового контура (b)

На рис. 5 представлены результаты измерения кондуктивных помех DC/DC-преобразователя (рис. 6) в диапазоне от 150 кГц до 108 МГц. Измерения проводились с помощью анализатора спектра Rohde & Schwarz. Желтые графики соответствуют пиковым значениям шумов, а синие графики относятся к средним значениям шумов. Как видно из графиков, преобразователь отвечает требованиям, предъявляемым к устройствам класса 5 в соответствии со стандартом CISPR 25. Предельно допустимые значения для устройств класса 5 согласно CISPR 25 отмечены красным цветом (пиковые значения на 20 дБ выше средних значений).

Рис. 8. Результаты измерений кондуктивных помех в соответствии с CISPR 25 в диапазоне от 150 кГц до 30 МГц (а) и в диапазоне от 30 МГц до 108 МГц (b)

Заключение

Переключения силовых транзисторов являются главными источниками кондуктивных и радиочастотных помех. В этой статье предложены советы по трассировке печатных плат, которые позволяют уменьшить уровень шумов, генерируемых DC/DC-преобразователями с дискретными МОП-транзисторами.

Для снижения уровня помех необходимо выполнять следующие рекомендации: уменьшать площадь силового контура, избегать разрывов и неоднородностей контуров тока, использовать четырехслойную печатную плату с внутренними слоями земли для экранирования (обеспечивает лучшую эффективность, чем двухслойная печатная плата), минимизировать длину проводников затворного контура управления и разводить их в виде дифференциальных пар, минимизировать площадь полигона узла коммутации SW для уменьшения емкостной связи.

Оптимизация трассировки печатной платы помогает улучшить показатели ЭМС без ущерба для эффективности или тепловых характеристик. В статье рассматривался пример понижающего синхронного преобразователя, однако аналогичный подход можно перенести на любую другую топологию. Для этого необходимо только правильно определить наиболее критичные контуры и воспользоваться предложенными рекомендациями при выполнении трассировки печатной платы.

Предыдущие главы:

- Руководство по электромагнитной совместимости в DC-DC-преобразователях. Часть 1: стандарты и измерения

- Руководство по электромагнитной совместимости в DC-DC-преобразователях. Часть 2: шумы и фильтрация

- Руководство по электромагнитной совместимости в DC-DC-преобразователях. Часть 3: паразитные параметры силового контура

- Руководство по электромагнитной совместимости в DC-DC-преобразователях. Часть 4: радиочастотные помехи

- Руководство по электромагнитной совместимости в DC/DC-преобразователях. Часть 5: борьба с помехами в схемах с интегральными преобразователями

Литература

- “The Engineer’s Guide to EMI in DC-DC Converters (Part 1): Standards Requirements and Measurement Techniques,” by Timothy Hegarty, How2Power Today, December 2017 issue.

- “The Engineer’s Guide to EMI in DC-DC Converters (Part 2): Noise Propagation and Filtering,” by Timothy Hegarty, How2Power Today, January 2018 issue.

- “The Engineer’s Guide to EMI in DC-DC Converters (Part 3): Understanding Power Stage Parasitics,” by Timothy Hegarty, How2Power Today, March 2018 issue.

- “The Engineer’s Guide to EMI in DC-DC Converters (Part 4): Radiated Emissions,” by Timothy Hegarty, How2Power Today, April 2018 issue.

- “The Engineer’s Guide To EMI In DC-DC Converters (Part 5): Mitigation Techniques Using Integrated FET Designs” by Timothy Hegarty, How2Power Today, June 2018 issue.

- LM5146-Q1-EVM12V automotive buck controller evaluation module with optional EMI shielding.

- “GaN Transistors for Efficient Power Conversion,” 2nd edition, by Alex Lidow et al., Wiley, September 2014.

- “Understanding the effect of PCB layout on circuit performance in a high frequency gallium nitride based point of load converter,” by David Reusch and Johan Strydom, APEC 2013, pp. 649-655.

- “Layout considerations for LMG5200 GaN power stage,” by Narendra Mehta, Texas Instruments application report SNVA729, 2015.

Опубликовано: 24.04.2019