Отладочная плата OpenEP2C5-C Standard на основе ПЛИС ALTERA FPGA серии Cyclon II и набора стандартных интерфейсов

OpenEP2C5-C Standard – отладочный комплект, состоящий из материнской платы DVK601 и платы ПЛИС CoreEP2C5. OpenEP2C5-C поддерживает дальнейшее расширение с использованием различных дополнительных плат функционального расширения для различных приложений. Модульность и открытый дизайн делают изделие идеальным для старта разработки приложений с серией ПЛИС FPGA ALTERA Cyclone II. OpenEP2C5-C позволяет быстро и легко начать проектирование с процессором NIOS II.

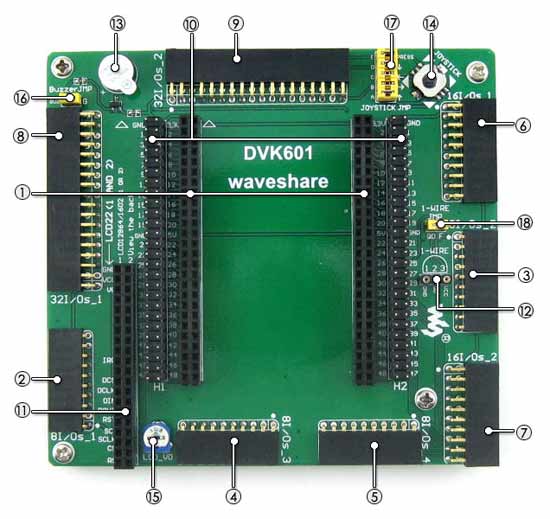

Рис. 1. Материнская плата DVK601

Отличительные особенности

Материнская плата DVK601:

- Разъем для подключения платы с ПЛИС FPGA или CPLD;

- 8I/Os_1 интерфейс, для подключения модулей (плат) расширения;

- 8I/Os_2 интерфейс, для подключения модулей (плат) расширения;

- 8I/Os_3 интерфейс, для подключения модулей (плат) расширения;

- 8I/Os_4 интерфейс, для подключения модулей (плат) расширения;

- 16I/Os_1 интерфейс, для подключения модулей (плат) расширения;

- 16I/Os_2 интерфейс, для подключения модулей (плат) расширения;

- 32I/Os_1 интерфейс, для подключения модулей (плат) расширения;

- 32I/Os_2 интерфейс, для подключения модулей (плат) расширения

Все интерфейсы, описанные выше:- способны работать как USART, I2C, SPI, PS/2 и т.д.,

- способны управлять такими приборами как FRAM, FLASH, USB, Ethernet и т.д.;

- FPGA разъем расширения:

- выводы FPGAдоступны на разъеме расширения,

- для подключения SDRAM платы;

- LCD interface, для подключения LCD22, LCD12864, LCD1602;

- ONE-WIRE interface: простое подключение к ONE-WIRE устройствам (корпус TO-92), например, к температурному датчику (DS18B20) и др.;

- Зуммер;

- Джойстик: пятипозиционный;

- Потенциометр: для управления задней подсветкой LCD22 или LCD12864, для управления контрастностью LCD1602;

- Джампер зуммера;

- Джампер джойстика;

- Джампер интерфейса ONE-WIRE

Для джамперов 16-18:- устанавливаются для подключения к I/Os (используется в демопримерах),

- снимаются для подключения к выводам, определяемым пользователем, посредством проводов-джамперов.

Плата DVK601 поддерживает широкий диапазон Core плат, при этом некоторые интерфейсные разъемы могут оказаться бесполезными. Например, при подключении Core3S250E '?8I/Os_3' и '?8I/Os_4' оказываются не подключенными.

CoreEP2C5:

Рис. 2. Плата CoreEP2C5

- ПЛИС EP2C5T144C8N: ALTERA Cyclone II FPGA со следующими параметрами:

- рабочая частота: 50 MHz,

- рабочее напряжение: 1.15 V?3.465 V,

- корпус: QFP144,

- I/O: 79,

- LEs: 4.6K,

- RAM: 120 kb,

- PLLs: 2,

- отладка/программирование: поддержка JTAG интерфейса;

- AMS1117-3.3, 3.3V - стабилизатор напряжения;

- AMS1117-1.2, 1.2V - стабилизатор напряжения;

- EPCS16, последовательная FLASH память , для хранения программы;

- Индикатор питания;

- Светодиоды;

- Кнопка сброса;

- 8. Кнопка nCONFIG: для реконфигурации чипа FPGA, эквивалент сброса по питанию;

- Переключатель питания;

- 50M кварцевый генератор;

- Разъем 5V DC;

- JTAG интерфейс: для отладки/программирования;

- Разъемы расширения FPGA: VCC, GNDи все порты I/Oдоступны на разъемах;

- LED джамперы, устанавливаются для управления светодиодами.

Примечание: Для работы с изделием требуется программатор/отладчик.

OpenEP2C5-C Standard поставляется с большим количеством демонстрационных программ (Таблица 1) для поддержки периферии, которые дают возможность быстрого старта для разработки собственных приложений.

Таблица 1.

| Периферия | Описание | Интерфейс | Verilog | VHDL | NIOS II C |

| S29GL128P | NorFLASH | 32I/Os |

|

| Y |

| AT24CXX | EEPROM | I2C | ? | ? | ? |

| FM24CXX | FRAM | I2C | ? | ? | ? |

| AT45DBXX | DATAFLASH | SPI |

|

| ? |

| SD card | FLASH | SPI |

|

| ? |

| H57V1262GTR | SDRAM | parallel |

|

| ? |

| PCF8563 | RTC | I2C |

|

| ? |

| DS18B20 | Temperature sensor | 1-WIRE | ? | ? | ? |

| SP3232 | Serial communication | UART | ? | ? | ? |

| SP3485 | Serial communication | UART | ? | ? | ? |

| PL2303 | USB TO UART | UART | ? | ? | ? |

| FT245 | USB TO FIFO | parallel |

|

| ? |

| CY7C68013A | USB DEVICE | I/Os |

| ? |

|

| ENC28J60 | Ethernet controller | SPI |

|

| ? |

| Buzzer | Sound device | 1I/O (PWM) | ? | ? | ? |

| PS/2 keyboard | Input device | PS/2 | ? |

| ? |

| Single buttons | Input device | ---- | ? | ? | ? |

| 4x4 keypad | Input device | 8I/Os | ? | ? | ? |

| Joystick | Input device | 5I/Os | ? | ? | ? |

| LED | Display device | ---- | ? | ? | ? |

| 8 SEG LED | Display device | 13I/Os | ? | ? | ? |

| VGA monitor | Display device | VGA | ? | ? |

|

| Character LCD | Display device | 11I/Os | ? | ? |

|

| Graphic LCD | Display device | 11I/Os | ? |

|

|

| 3.2 inchmulti-color LCD + touch screen | Display device + Input device | 32I/Os |

|

| ? |

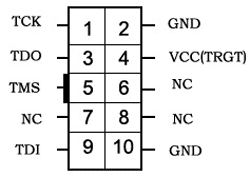

Сигналы JTAG интерфейса OpenEP2C5-С (См. Таблицу 2 и Рис. 3)

Таблица 2. Сигналы JTAG интерфейса

| Pin | Signal Name | Description |

| 1 | TCK | Clock signal |

| 2 | GND | Signal ground |

| 3 | TDO | Data from device |

| 4 | VCC(TRGT) | Target power supply |

| 5 | TMS | JTAG state machine control |

| 6 | NC | No connect |

| 7 | NC | No connect |

| 8 | NC | No connect |

| 9 | TDI | Data to device |

| 10 | GND | Signal ground |

Рис. 3. JTAG интерфейс OpenEP2C5-С

Документацию и программное обеспечение можно найти на сайте производителя.

Анонс составил и подготовил

Шрага Александр,

office@terraelectronica.ru

Производители: Wvshare

Опубликовано: 21.07.2016