Использование встраиваемых ядер eFPGA при создании SOC-микросхем

ПЛИС (FPGA) являются незаменимым инструментом при создании уникальных и высокопроизводительных решений, функционал которых при необходимости удается легко изменять. С помощью ПЛИС можно даже реализовывать программные процессорные ядра, хотя аппаратные процессоры оказываются более эффективными. Неудивительно, что крупные производители FPGA, такие как Microsemi, Altera и Xilinx, создали ПЛИС со встроенными аппаратными процессорами. О таких решениях можно прочитать, например, в статье «FPGA Packs In Dual Cortex-A9 Micro».

Так почему бы не пойти дальше и не включить ПЛИС в состав специализированных SoC-микросхем (system-on-chip)? На этот вопрос ответила компания Menta с ее новым продуктом – eFPGA.

Мне удалось поговорить с директором по развитию Menta – Жаном Луи Бреле. Он рассказал об eFPGA и о том, как их можно встраивать в SoC. Далее представлена текстовая версия нашего интервью.

Вонг: Что такое eFPGA?

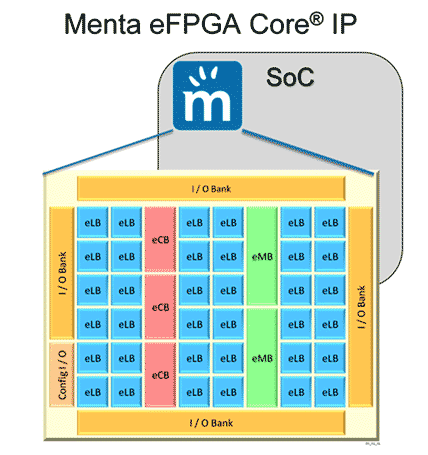

Бреле: eFPGA – это программируемая логическая интегральная схема, которая встраивается в SoC в виде IP-ядра наравне с другими аппаратными и программными блоками (рис. 1). При этом конечный функционал eFPGA может быть определен уже после изготовления SoC. Это позволяет разработчикам и производителям вносить изменения в структуру и функционал SoC в любое удобное время. Таким образом, удается избавиться от расходов, связанных с повторным производством чипов микросхем.

Рис. 1. IP-ядро eFPGA встраивается в SoC наравне с другими аппаратными и программными блоками

Вонг: Зачем использовать eFPGA, если вы уже разрабатываете собственный чип?

Бреле: eFPGA обеспечивает значительную гибкость – при необходимости с помощью eFPGA удается модифицировать аппаратную часть SoC. С точки зрения проектирования, такое решение экономит много времени, так как возможность программного изменения SoC позволяет повторно использовать существующие наработки и настраивать одну и ту же SoC с учетом особенностей различных приложений и устройств, а также в соответствии с требованиями рынка. Это экономит средства и позволяет продуктам быстрее выходить на рынок.

Подобный подход также позволяет изготавливать чип SoC еще до того, как все функции и структура микросхемы будут определены. Например, реализация поддержки определенных стандартов или функций безопасности (криптографических протоколов) в eFPGA может быть выполнена после производства. Кроме того, если с течением времени протоколы поменяются, то разработчик сможет просто обновить SoC вместо того, чтобы начинать проектирование с нуля.

Вонг: Как происходит конфигурация eFPGA и насколько большой/ маленькой может быть eFPGA?

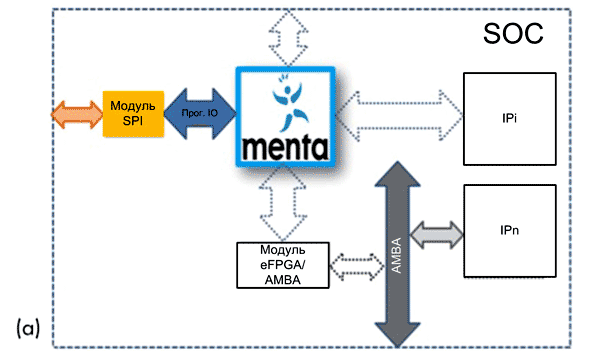

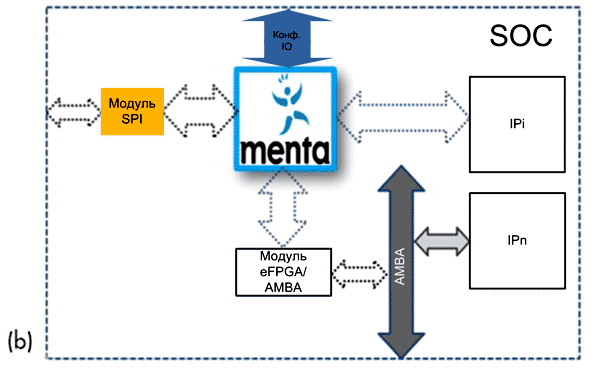

Бреле: Формат программирования eFPGA определяется разработчиком. Возможна реализация как внутреннего, так и внешнего программирования. В частности, для выполнения внешнего программирования можно использовать последовательный SPI-интерфейс (рис. 2а) или более скоростной параллельный интерфейс (рис. 2б). В последнем случае расплатой за быстродействие станет увеличение числа занятых контактов микросхемы. Внутреннее программирование может быть выполнено либо напрямую, либо через внутреннюю шину.

|  |

| Рис. 2. eFPGA могут быть запрограммированы с помощью последовательного SPI-интерфейса (a) или с помощью параллельного интерфейса (b) | |

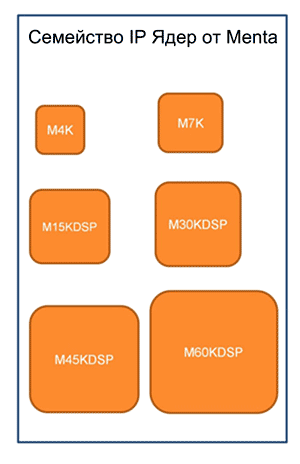

Теоретически, размеры eFPGA не ограничены и выбираются, исходя из существующих потребностей. Однако выбор слишком маленького размера может привести к ограничению функционала, а выбор слишком большого размера поставит под угрозу производительность. Новое семейство IP-ядер Menta включает шесть готовых опций eFPGA, которые содержат от 4 до 60 тыс. эквивалентных вентилей ASIC, плюс блоки DSP (рис. 3). Ядра IP поставляются в виде макросов с оптимизированными размерами массивов для встроенных логических блоков (eLB), встроенных пользовательских блоков (eCB) и встроенных блоков памяти (eMB), каждый из которых имеет возможность настройки с учетом требований рынка или конкретных приложений. По требованию заказчика могут быть разработаны и нестандартные исполнения eFPGA.

Рис. 3. Семейство IP-ядер eFPGA от Menta

Вонг: Какие инструменты доступны для программирования eFPGA?

Бреле: Menta разработала собственный инструмент программирования под названием Origami programmer. Этот инструмент обеспечивает полный цикл программирования: интерпретацию HDL, роутинг и размещение функциональных блоков по eFPGA, организацию битового потока при прошивке. Origami programmer имеет поддержку VHDL, Verilog, SystemVerilog и SDC (Synopsis Design Constraints). Кроме того, разработчики получают дополнительные инструменты для выполнения временного моделирования.

Вонг: Можно ли для программирования eFPGA использовать встроенный процессор?

Бреле: Я уже коснулся этой темы, отвечая на второй вопрос. Да, для программирования eFPGA можно использовать встроенный процессор. В таком случае процессор взаимодействует с eFPGA либо напрямую, либо через шину, например, AMBA.

Вонг: Каковы основные области применения для eFPGA?

Бреле: eFPGA особенно хорошо подходят для приложений, требующих интенсивных параллельных вычислений. В качестве примера можно привести радиолокационные устройства в аэрокосмических и оборонных системах, а также системы обработки видео. Кроме того, возможность вносить обновления в структуру микросхемы после производства или в полевых условиях делает eFPGA идеальным выбором для SOC, используемых для шифрования. eFPGA также будут актуальны для SoC, которые необходимо модифицировать с учетом изменений, вносимых в стандарты. Это касается практически всех отраслей, в том числе автомобильной, промышленной и бытовой электроники.

Вонг: Можете ли Вы подробнее рассказать о самой компании Menta?

Бреле: Menta является частной компанией, расположенной во Франции в городе Монпелье. Компания предоставляет готовые eFPGA-решения и решения, основанные на индивидуальных требованиях заказчика, для ASIC или SiP-микросхем. Наша программируемая логика использует масштабируемую, настраиваемую и легко программируемую архитектуру, которая обеспечивает гибкость настройки для ASIC следующего поколения.

Опубликовано: 10.01.2019