Отладочный набор Terasic TR4 FPGA

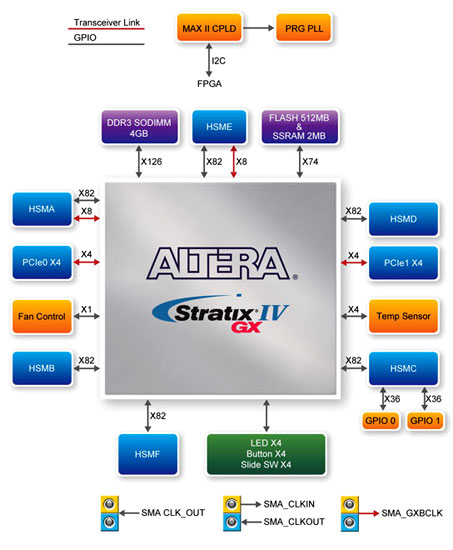

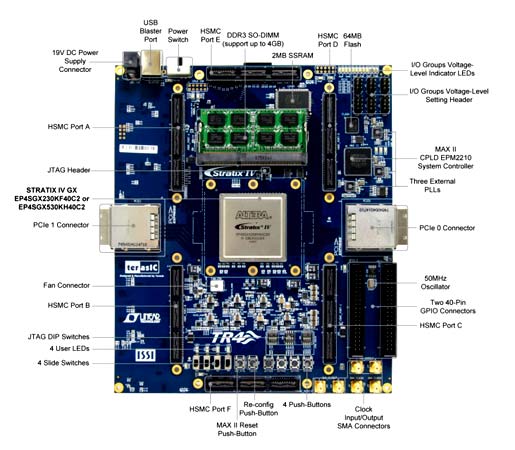

P0107 – отладочная плата TR4 набора P0107 представляет собой великолепную аппаратную платформу для системного дизайна, требующего высокой производительности, последовательного подключения и расширенного взаимодействия с памятью.

Разработанная специально для удовлетворения быстро меняющихся требований на многих высокотехнологичных рынках в отношении большей полосы пропускания, улучшенных параметров фазового дрожания фронтов цифровых сигналов (джиттера) и более низкого энергопотребления, плата TR4 создана на базе микросхемы подсемейства ПЛИС FPGA Stratix® IV GX и поддерживается стандартными в отрасли периферийными устройствами, разъемами и интерфейсами, которые предлагают богатый набор функций, который подходит для широкого спектра ресурсоемких приложений.

Преимущества платформы Stratix® IV GX FPGA со встроенными трансиверами позволили TR4 полностью соответствовать версии 2.0 стандарта PCI Express, что способно ускорить массовую разработку приложений на основе PCI Express и позволить заказчикам развертывать проекты для широкого спектра приложений высокоскоростной связи.

TR4 поддерживается несколькими референс-дизайнами, имеет шесть разъемов высокоскоростной мезонинной карты (HSMC - High-Speed Mezzanine Card), что делает возможным масштабирование и кастомизацию с помощью дочерних мезонинных плат. Для крупномасштабной разработки прототипов ASIC можно объединить несколько TR4 для создания легко настраиваемой системы с несколькими ПЛИС FPGA.

Спецификация

FPGA микросхемы

- Stratix IV GX EP4SGX230

- 228 000 логических элементов (LE)

- 17,133 КБит общей памяти

- 1 288 блоков умножителей, 18x18 бит

- 2 PCI Express hard IP-блока

- 744 пользовательских линий ввода / вывода

- 8 цепей ФАПЧ (PLL)

- Stratix IV GX EP4SGX530

- 531 200 логических элементов (LE)

- 27 376 кбит памяти

- 1024 блоков умножителей 18x18-бит

- 4 hard IP-блока PCI Express

- 744 пользовательских линий ввода / вывода

- 8 цепей ФАПЧ (PLL)

Конфигурация FPGA

- Системный контроллер MAXII CPLD EPM2210 и быстрая пассивная параллельная (FPP) конфигурация

- Встроенный USB-бластер для использования с Quartus II программатором

- Программируемая микросхема синхронизации PLL, настроенная через MAX II CPLD

- Поддержка режима JTAG

Микросхемы памяти

- 64 МБ флэш-памяти с 16-битной шиной данных

- SSRAM 2 МБ (512 К x 32)

Сокет DDR3 SO-DIMM

- Емкость до 8 ГБ

- Максимальная тактовая частота памяти 533 МГц

- Теоретическая пропускная способность до 68 Гбит/с

Кнопки, переключатели и светодиоды

- 4 управляемых пользователем светодиода

- 4 пользовательские кнопки

- 4 пользовательских ползунковых переключателя

Встроенное тактирование

- Генератор с частотой 50 МГц

SMA разъемы

- Пара разъемов SMA для дифференциальных тактовых входов

- Пара разъемов SMA для дифференциальных тактовых выходов

- SMA разъем для выхода тактирования

- SMA разъем для внешнего тактового сигнала

Два разъема PCI Express x4

- Поддержка скорости подключения Gen1 2.5 Гбит/с на полосу до Gen2 со скоростью 5.0 Гбит/с на полосу

- Высокоскоростные трансиверные каналы до 6/5 Гбит/с

- Поддержка нисходящего режима

Шесть 172-контактных высокоскоростных мезонинных карт (HSMC)

- 6 разъемов HSMC

- Настраиваемые стандарты линий ввода/вывода – 1.5 В, 1.8 В, 2.5 В, 3.0 В

- 16 высокоскоростных трансиверов до 6.5 Гбит/ с

- Среди портов HSMC от A до D имеется 55 истинных каналов передачи LVDS до 1.6 Гбит/с и 17 эмулированных каналов передачи LVDS до 1.1 Гбит/с

Два 40-контактных разъема расширения

- 72 вывода I/O FPGA; 4 линии питания и земли

- Настраиваемые стандарты линий ввода/вывода – 1.5 В, 1.8 В, 2.5 В, 3.0 В

- Делит контакты с портом HSMC

Питание

- Автономный вход постоянного тока 19 В

Изделие TR4 сопровождается целым рядом инструментов, среди которых:

- TR4 System Builder - мощный инструмент, который позволит пользователям создавать файлы проекта Quartus II с индивидуальным дизайном для платы TR4. TR4 System Builder автоматически может генерировать файл проекта верхнего уровня, назначать выводы, устанавливать стандартные настройки ввода/ вывода для платы TR4. Кроме того, с помощью TR4 System Builder через разъемы HSMC пользователь может выбирать различные дочерние карты.

- Панель управления TR4 - позволяет пользователям получать доступ к различным компонентам на плате TR4 с хост-компьютера.

Отличительные особенности:

- ПЛИС:

- Altera Stratix® IV GX FPGA (EP4SGX230C2/EP4SGX530C2);

- Элементы конфигурации и настройки:

- Встроенная схема USB Blaster для программирования

- Быстрая пассивная параллельная конфигурация (FPP) через MAX II CPLD и FLASH

- Компоненты и интерфейсы:

- Шесть разъемов HSMC (два с поддержкой трансивера)

- Два 40-контактных разъема расширения GPIO (общие контакты с HSMC портом C)

- Два внешних разъема PCI Express 2.0 (x4 полосы)

- Память:

- DDR3 SO-DIMM сокет (8ГБ Макс.)

- 64МБ FLASH

- 2МБ SSRAM (синхронная статическая память произвольного доступа)

- Входной/выходной пользовательский интерфейс общего назначения:

- Четыре светодиода

- Четыре кнопки

- Четыре ползунковых переключателя

- Система тактирования:

- Встроенный 50 МГц генератор

- Три встроенных программируемых чипа PLL синхронизации

- Пара разъемов SMA для дифференциального тактового входа

- Пара разъемов SMA для дифференциального тактового выхода

- Разъем SMA для входа внешнего тактового сигнала

- SMA разъем для тактового выхода

- Питание:

- 19 В вход DC

- Другое:

- Температурный датчик

- Вентилятор охлаждения FPGA

Страница изделия на сайте производителя.

Производители: Terasic

Опубликовано: 10.04.2020